您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這期內容當中小編將會給大家帶來有關基于FPGA硬件的網絡設計是怎么樣的,文章內容豐富且以專業的角度為大家分析和敘述,閱讀完這篇文章希望大家可以有所收獲。

引言

很久沒有看基于FPGA的神經網絡實現的文章了,因為神經網絡加速設計做的久了就會發現,其實架構都差不多。大家都主要集中于去提高以下幾種性能:FPGA算力,網絡精度,網絡模型大小。FPGA架構也差不多這幾個模塊:片上緩存,卷積加速模塊,pool模塊,load,save,指令控制模塊。硬件架構上并不是太難,難的反而是軟件編譯這塊。因為其要去適應不同的網絡模型,還要能兼容FPGA硬件的變化,同時要為客戶提供一個容易操作的接口。這些在目前情景下還比較困難。首先是FPGA硬件的變化太多,各個模塊可配參數的變化(比如卷積模塊并行數的變化),另外一個是網絡模型多種多樣以及開源的網絡模型平臺也很多(tensorflow,pytorch等)。網絡壓縮也有很多種算法,這些算法基本上都會導致網絡模型精度的降低。一般基于FPGA的網絡加速設計都會強調模型被壓縮了多少以及FPGA上可以跑得多快,卻很少集中于去改善精度。

這篇文獻從概念上提出了硬件和網絡的協同設計,是很好的一個思路。因為之前神經網絡加速硬件設計和網絡壓縮是分開的,只是在網絡壓縮的時候盡可能考慮到硬件的特點,讓網絡模型更加適合硬件架構。這篇論文其實也是在做這樣類似的工作,我并不認為它真正的實現了硬件和網絡設計的協同(雖然其標榜自己如此)。但是它確實給我們提供了一個新的研究思路:如何從一開始就設計一個能夠適用于硬件的網絡。好的,廢話不多說,來看論文。

1. 來自作者的批判

發表論文,總是要先去總結以往論文的優缺點,然后指出其中不足,凸顯自己的優勢。這篇文章也花費了很大篇幅來批判了過去研究的不足。總結起來有以下幾點:

1) 過去的研究都是用一些老的網絡,比如VGG,resnet,alexnet等,這些網絡已經落伍了,市場上已經不怎么用了;

2) 過去用的數據集也小,比如CIFAR10這類,包含的圖片種類和數量都太少,不太適合商業應用;

3) 壓縮老的網絡的技術手段不再適用于最新的網絡,比如像squeezeNet網絡,它就比alexnet網絡小50倍,但是能達到和alexnet一樣的精度;

4) 以往的類似resnet的網絡,有skip連接的,并不適合在FPGA上部署,因為增加了數據遷移;

5) 以往網絡的卷積核較大,如3x3,5x5等,也不適合硬件加速;

6) 以前網絡壓縮集中于老的那些網絡,這些網絡本身就有很大的冗余,所以壓縮起來很容易,而最新的網絡比如ShuffleNet等壓縮起來就沒有那么容易了,但是這樣的報道很少;

總之,意思就是之前的文章都撿軟柿子捏,而且比較落后了。那么我們來看看在這樣狂妄口氣之下的成果如何。

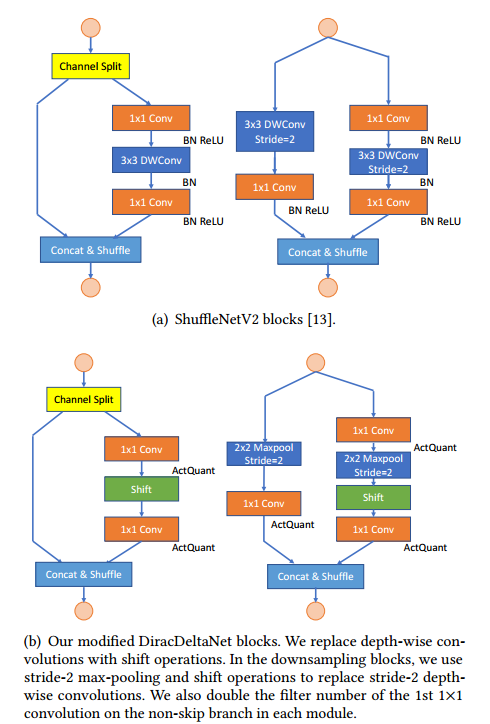

2. shuffleNetV2到DiracDeltNet

shuffleNetV2是新發展出來的一個神經網絡,它的網絡模型中參數更小(比VGG16小60倍),但是精度只比VGG16低2%。shuffleNet不再像resnet將skip連接的數據求和,而是skip連接的數據進行concat,這樣的操作降低了加法操作。Skip連接可以擴展網絡的深度和提高深層網絡精度。但是加法skip不利于FPGA實現,一個是加法消耗資源和時間,另外一個是skip數據增加了遷移時間。Concat連接也和加法skip有相同的功能,增加網絡深度和精度。

作者對shuffleNetV2網絡結構進行了更有利于FPGA部署的微調。有以下三個方面:

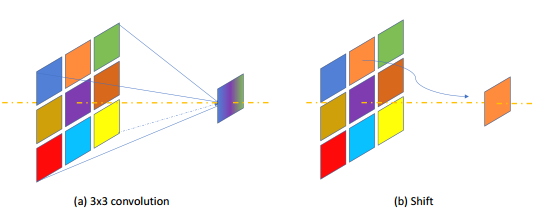

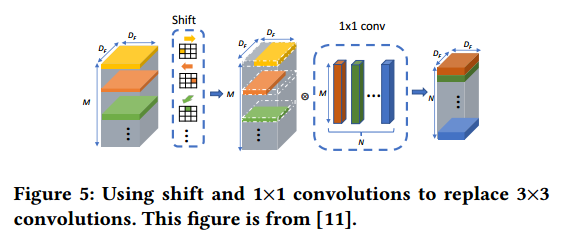

1) 將所有3x3卷積(包括3x3depth-wise卷積)都替換為shift和1x1卷積。這樣替換是能夠降低feature map數據的遷移,比如3x3的卷積每個圖像數據要使用3次,而1x1只需要搬移一次,降低了邏輯復雜性,也提高了運算速度。Shift操作是將某個范圍的pixel移動到中間作為結果,這樣的操作減少了乘法運算次數。這種替換會導致精度降低,但是可以減少FPGA運算次數。

2) 將3x3的maxpooling操作降低為2x2的。

3) 調整了channel的順序來適應FPGA。

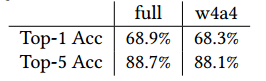

3. 量化

為了進一步降低網絡參數量,作者采用了DoReFa-Net網絡的量化方式,對全精度權重進行了量化。同時作者還對activation進行了量化。量化結果如下:

精度損失很小。

文獻中使用了很多對網絡修改的微調技術,細節很多,可以看出對這樣一個已經很少參數的網絡來說,要進一步壓縮確實要花費很大功夫。這可能不太具有普遍性。這些微調應該會花費很多時間和精力。

4. 硬件架構

硬件主要實現的操作很少,只有一下幾種:

1)1x1卷積

2)2x2的ma-pooling

3)shift

4)shuffle和concat

所以硬件架構上也變得很簡潔,作者在文章中說兩個人用HLS只做了一個月。

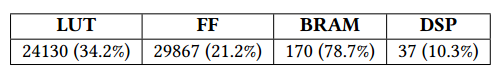

使用資源很少。

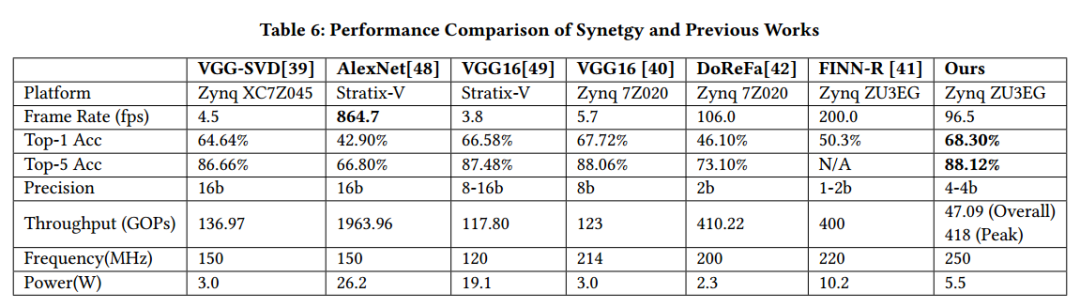

看以下和其他人的結果對比:

上述就是小編為大家分享的基于FPGA硬件的網絡設計是怎么樣的了,如果剛好有類似的疑惑,不妨參照上述分析進行理解。如果想知道更多相關知識,歡迎關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。