您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇文章為大家展示了如何實現sparc處理器淺析,內容簡明扼要并且容易理解,絕對能使你眼前一亮,通過這篇文章的詳細介紹希望你能有所收獲。

前幾天我看到知乎上的一篇文章《時代的眼淚:繁華落盡的SPARC處理器》,大致上講述了一下Sun公司的UltraSPARC處理器,那時左批HP,右打IBM,儼然一副高高在上的氣勢。我覺得關于SPARC如何一步一步從繁榮走向平淡,又是如何在歷史長河中發揮出濃墨重彩的一筆,我就不贅述了。這篇文章主要想講一些sparc體系相關的問題。目前,sparc出現在我們視野中并不多見,其實利用sparc處理器一直是航天上面在使用,由于其特殊的架構以及目前美國對中國的態勢,sparc架構在航天、飛機、雷達領域的利用也是越來越重要了。目前北京微電子技術研究所出來幾款SPARC V8架構的芯片。其中BM3803是基于SPARC V8體系結構的32位精簡指令集的國產嵌入式芯片,其特點是功能強、可靠性高、低功耗等等。下面從系統啟動、窗口寄存器、中斷處理這三部分看一看sparc v8處理器的特點。

一般我們做嵌入式開發都是用C語言編寫實現,但是實際情況是在系統上電的之后,一般往往會執行一段初始化的匯編代碼,可以理解為系統的BIOS。對于sparc v8架構的bm3803處理器來說,地址分配的空間如下:

| 地址 | 作用 |

|---|---|

| 0x00000000-0x1FFFFFFF | PROM |

| 0x20000000-0x3FFFFFFF | I/O |

| 0x40000000-0x7FFFFFFF | SRAM |

一般芯片啟動后,執行的代碼都是在0地址處,所以固話的代碼放在PROM的0地址空間。

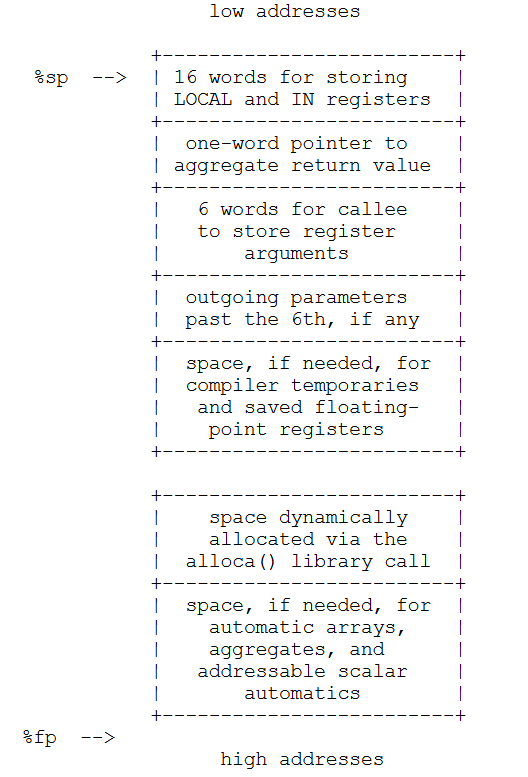

需要設置C語言可以執行的棧空間以及清除bss段。其中棧的布局可以參考如下:

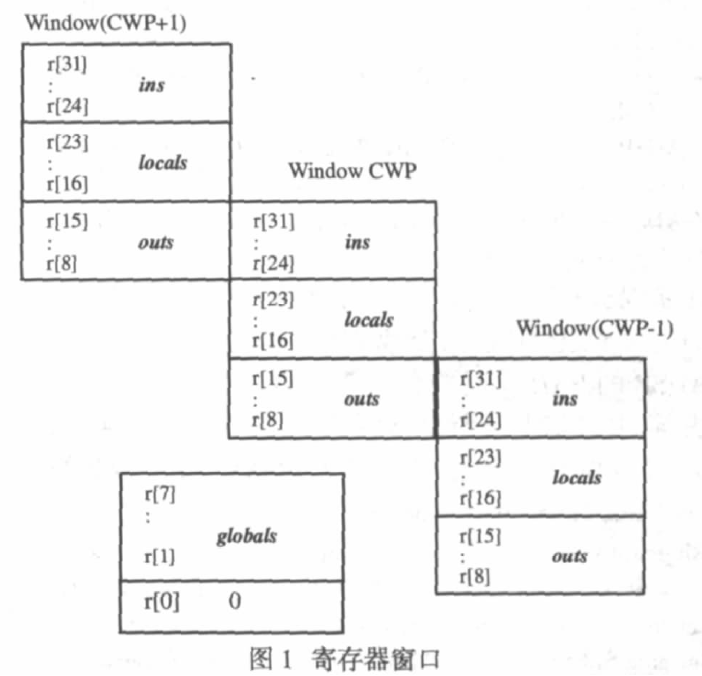

由于sparc架構集成伯克利RISC結構,所以窗口寄存器是一個非常重要的特性。也就是說,一個窗口寄存器組只對當前的程序可見。而一個寄存器窗口又包括32個無浮點的寄存器。

| Register Group | Mnemonic | Register Address |

|---|---|---|

| global | %g0-%g7 | r[0]-r[7] |

| out | %o0-%o7 | r[8]-r[15] |

| local | %l0-%l7 | r[16]-r[23] |

| in | %i0-%i7 | r[24]-r[31] |

其中SPARC結構規定了一共可以有N個寄存器的窗口,N=2^n(1=<n<=5),即N=2、4、8、16、32。

當執行SAVE指令的時候,會分配一個全新的串口CWP-1。當RESTORE指令的時候,則CWP+1。其中比較有特點是,兩個窗口是有8個寄存器公用的,也就是上一個窗口的out為下個窗口的in。這樣可以提高程序的執行效率,不用每次都處理所有的寄存器。

一般來說,sparc上的特殊寄存器需要注意的是處理器狀態寄存器(Processor State Register),名稱為%PSR。以及無效窗口標識(Widows Invalid Register),名稱為%WIM。

其中PSR主要控制CWP窗口操作、中斷處理開關、以及Trap的處理。

WIM是無效窗口,BIT0~BIT7分別對應窗口0~7,在CPU的8個寄存器窗口中只能存在一個窗口為無效窗口。

在sparc處理中斷和陷阱的時候,也是首先需要一個trap的地址。一般進入中斷后,會進入另外的一個模式,也就是說會開辟一個新的窗口,比如我們做任務切換的時候。sparc是由軟中斷(TA指令)實現。SPARC架構是不支持直接對PC指針進行操作的,而是CPU在發生中斷的時候會將當前的PC、NPC寫到寄存器%l1,%l2寄存器中。在中斷結束返回的時候,CPU自動將%l1,%l2內容寫到PC、NPC。這樣就實現了一個任務的切換過程。

當發生中斷的嵌套的時候,也是需要通過中斷棧來實現當前現場的保存。

上述內容就是如何實現sparc處理器淺析,你們學到知識或技能了嗎?如果還想學到更多技能或者豐富自己的知識儲備,歡迎關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。