您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇文章給大家分享的是有關大數據異步復位網絡中同步和分配的挑戰和解決方案是什么,小編覺得挺實用的,因此分享給大家學習,希望大家閱讀完這篇文章后可以有所收獲,話不多說,跟著小編一起來看看吧。

異步復位和同步時鐘之間缺乏協調會導致設計出現故障。

在VLSI設計中,異步復位用于在上電后將同步電路復位成已知狀態。在大規模的多時鐘域設計中,這種問題會惡化。

除了同步(synchronization)問題之外,向設計中數百萬個觸發器分配(distribution)異步復位也具有挑戰性,需要類似于CTS(時鐘樹綜合)的技術。

Asynchronous reset challenges

同步復位需要有效時鐘,可能會影響數據路徑的時序。同步復位是確定性的,不會導致亞穩態。

異步復位不需要有效時鐘,可以利用不影響數據路徑時序的特殊觸發器輸入引腳。但是,異步復位可能導致觸發器中的亞穩態。

在許多情況下,異步復位可以由同步復位替換,但在某些情況下,必須使用異步復位。比如說在上電時沒有時鐘或被門控以降低功耗,但需要為其外部接口提供已知狀態。

在異步復位置位期間,可以忽略時鐘和復位之間的時序,但異步復位釋放必須與時鐘同步。如果異步復位在時鐘邊沿釋放可能導致亞穩態。

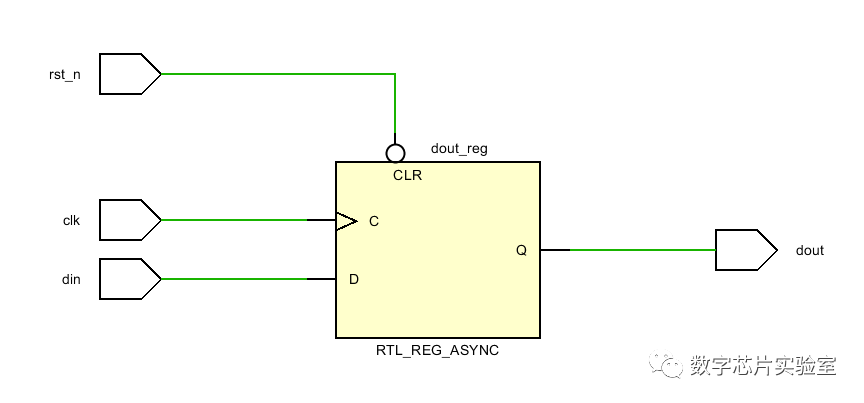

如上圖所示為高電平有效的異步復位。復位在時間a處置位,并在確定的傳播延遲TR-pd后影響觸發器的輸出Q,不關心此時時鐘的狀態。復位在時間b處釋放,RST端口相對于時鐘端口CLK必須滿足恢復和移除時間( recovery和removal timing),否則觸發器會變為亞穩態,從而可能導致設計故障。這種情況類似于違反觸發器數據端口D的建立和保持時間。

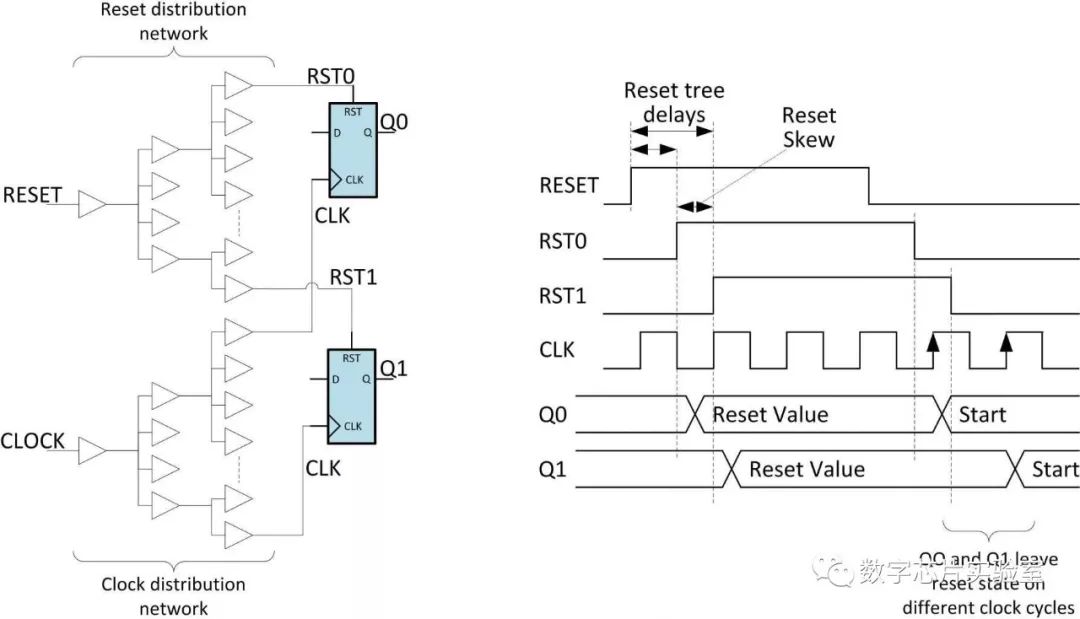

此外,對于大型設計,由于設計中不相等的導線長度、負載和IR drop和工藝偏差,復位和時鐘分配網絡( reset and clock distribution networks )的偏斜可能很大。在這種情況下,設計的不同部分可能在不同的時鐘周期進行復位,從而沒有實現預期的功能。

上圖中,RESET在不同的時鐘周期到達觸發器Q0和Q1,導致觸發器在不同的時鐘周期進行復位和釋放。

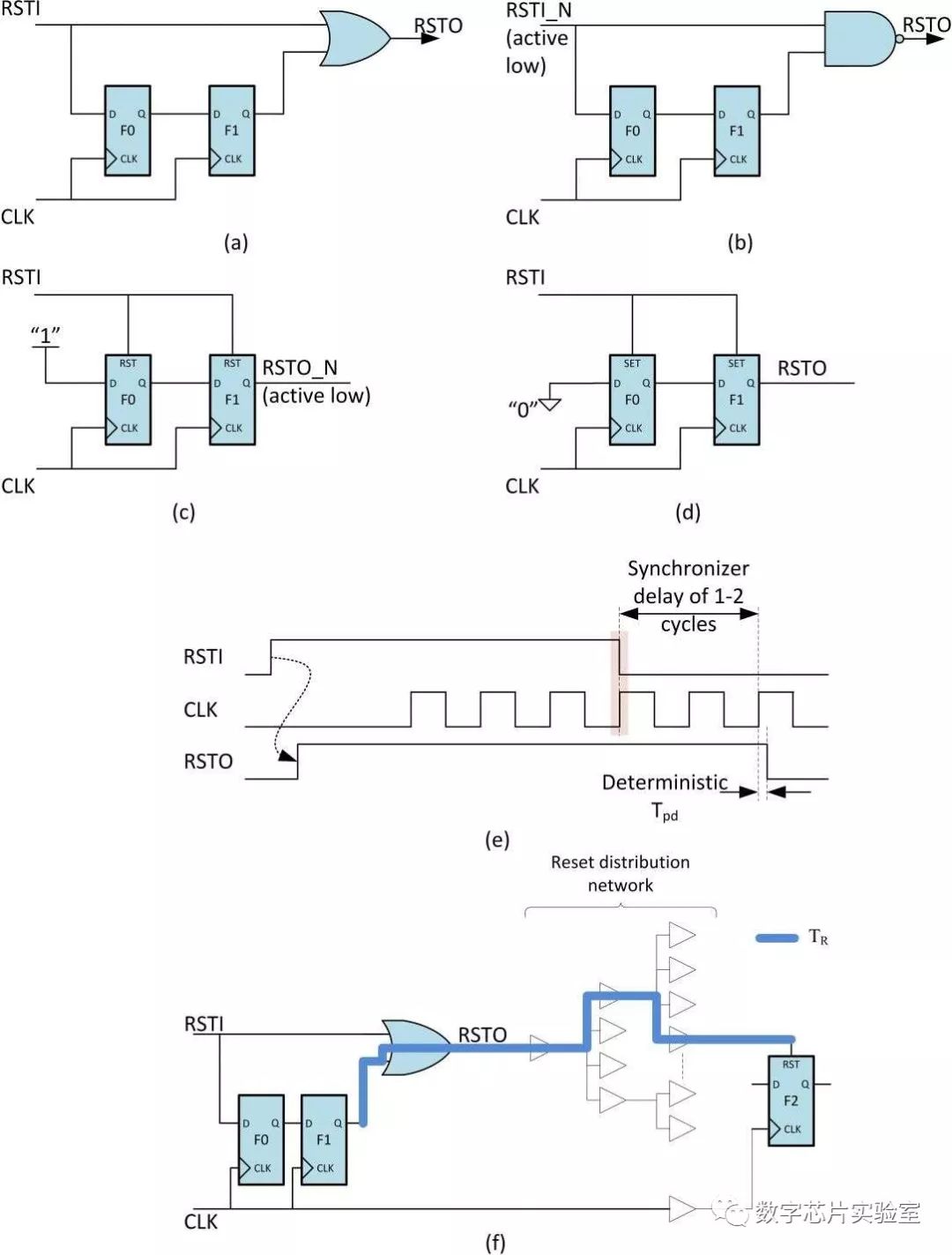

為避免上述問題,必須將異步復位的釋放同步到目標時鐘。傳統的方案是在復位分配網絡的根處使用復位同步器。如下圖所示

如圖a和圖b所示,輸入的異步復位RSTI信號通過組合邏輯連接到同步器輸出RSTO。因此,RSTO的置位不依賴于時鐘。

圖a的同步器中,RSTI和RSTO都是高電平有效信號,而圖b的同步器中,輸入RSTI_N是低電平有效信號,RSTO是高電平有效。在RSTI的異步釋放時,通過兩級觸發器(F0,F1)進行同步。然后,RSTO被同步釋放。

復位同步器的操作如圖e的波形圖所示。在同步時,由于F0觸發器可能存在亞穩態,復位釋放的延遲可能會存在一個時鐘周期的變化。同步器中采用的觸發器數量應根據MTBF計算設置,由于RSTI速率非常低,在大多數情況下,兩個觸發器可以提供令人滿意的MTBF。

圖c和圖d顯示了異步復位同步器的另一種常見風格。采用了具有異步復位/置位端口的觸發器,之前的同步器采用了沒有RST / SET端口的簡單D觸發器。圖c在RSTI置位時,無論時鐘如何,同步器RSTO_N(低電平有效)的輸出都會異步地變為有效。在RSTI釋放時,觸發器F0的D端口連接到VDD信號(“1”)。然而,F0可能變為亞穩態,因為F1的輸入在第一個時鐘邊沿沒有變化,F1不受亞穩態的影響。因此,使用雙觸發器同步器使常數“1”輸入同步,從而導致RSTO_N的同步釋放。

圖c和圖d的同步器可以在沒有時鐘的情況下工作,即時鐘可以在RSTI釋放之后出現。在RSTI釋放之前,圖a和圖b同步器需要一個穩定的時鐘在復位釋放前初始化內部觸發器。

圖f是同步器觸發器F1和目標應用觸發器F2之間的復位路徑。可以看出,由于兩個觸發器F1 F2都位于同一時鐘域,因此路徑TR應根據STA進行優化,即應短于時鐘周期,并滿足所有目的觸發器(例如F2)的恢復和移除時間檢查。

將復位分配網絡延遲表示為TR,將時鐘周期表示為TCLK,設計應滿足以下表達式(忽略時鐘偏差):

TCLK >= TR+ TSU … (1)

顯然,在以下情況下,復位分配網絡的時序收斂具有挑戰性:

大型復位分配網絡。當時鐘域內觸發器的數量很大時,復位分配網絡路徑延時時間TR變大,可能大于單個時鐘周期,因此違反了時序約束(1)。

高速的時鐘頻率。當采用快速時鐘時,時鐘周期TCLK變短,時序收斂(1)具有挑戰性。

具有大量觸發器并在高頻下工作的高性能設計需要用于處理復位分配網絡的特殊解決方案。根據表達式(1)的優化需要類似于時鐘樹合成(CTS, Clock Tree Synthesis )的優化算法。

CTS和復位樹綜合之間的主要區別在于復位樹綜合缺少 low skew要求,只要滿足約束(1)即可。

對于ASIC設計,這種方法由大量的大buffer組成。在FPGA設計中,則需要占用 global net資源。

復位樹綜合在復位切換期間需要額外的功耗。考慮到異步復位很少使用 - 通常在每次上電時使用一次。高扇出全局網絡導致的功耗、面積、走線資源和EDA的run time都是不必要的代價。

為了滿足高扇出網絡的時序,綜合工具傾向于復制路徑中的源觸發器,以減少復制后的觸發器的扇出。雖然這種方法在功能上對于常規同步邏輯是正確的,但是當考慮異步復位網絡時,可能導致功能故障和 降低異步復位網絡的可靠性。

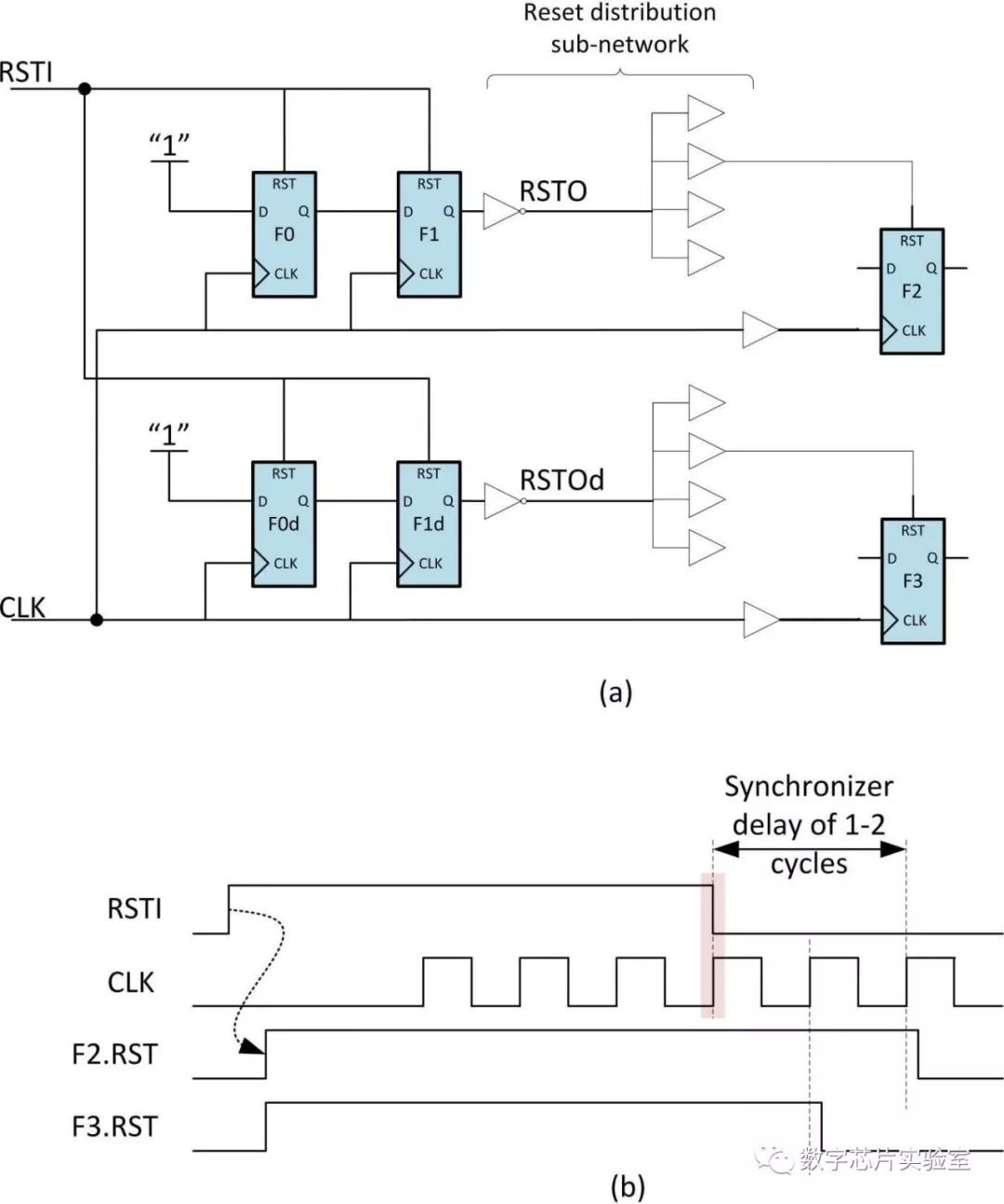

如上圖所示,圖a中對復位同步器進行復制。全局復位網絡分為兩個子網絡,分別包含{F1,F2}和{F1d,F3}路徑。

RSTI異步輸入分別由兩個不同的同步器同步,每個同步器產生隨機延遲。因此,即使RSTI在兩個同步器輸入處同時改變,RSTO和RSTOd輸出也可以相隔一個時鐘周期,導致觸發器F2和F3并非同步復位釋放。

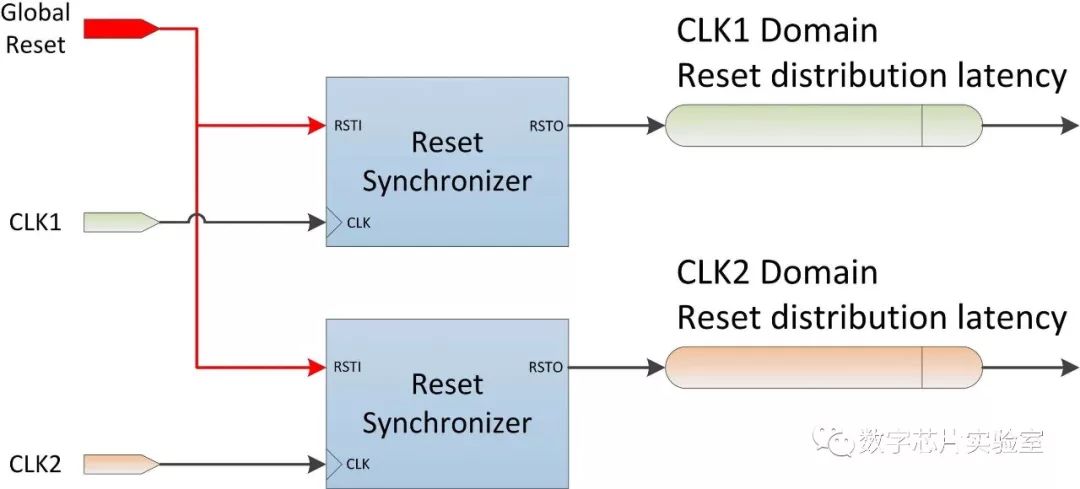

在多時鐘域設計中,異步復位應分別被每個時鐘域同步,如上圖所示。由于不同的時鐘域包含不同數量的觸發器,因此它們的復位分配網絡延遲不相等。

每個復位同步器都會產生額外的非確定性延遲,因此使整個多時鐘域設計的同時復位釋放變得不切實際。

可以定義復位釋放順序以確保正確的復位操作。例如,M2模塊的復位在M1模塊復位之后,然后M1開始向M2發送數據。

以上就是大數據異步復位網絡中同步和分配的挑戰和解決方案是什么,小編相信有部分知識點可能是我們日常工作會見到或用到的。希望你能通過這篇文章學到更多知識。更多詳情敬請關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。