您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這篇文章主要介紹“Verilog設計方法及流程是什么”,在日常操作中,相信很多人在Verilog設計方法及流程是什么問題上存在疑惑,小編查閱了各式資料,整理出簡單好用的操作方法,希望對大家解答”Verilog設計方法及流程是什么”的疑惑有所幫助!接下來,請跟著小編一起來學習吧!

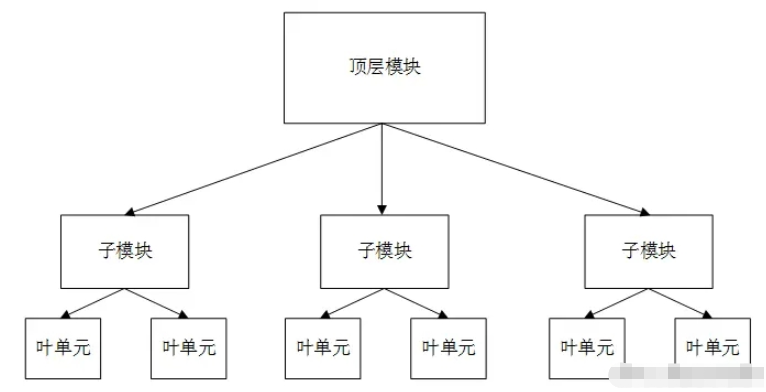

Verilog 的設計多采用自上而下的設計方法(top-down)。即先定義頂層模塊功能,進而分析要構成頂層模塊的必要子模塊;然后進一步對各個模塊進行分解、設計,直到到達無法進一步分解的底層功能塊。這樣,可以把一個較大的系統,細化成多個小系統,從時間、工作量上分配給更多的人員去設計,從而提高了設計速度,縮短了開發周期。

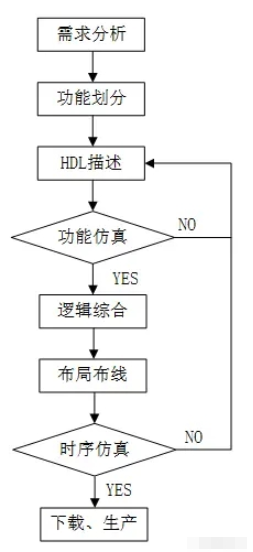

Verilog 的設計流程,一般包括以下幾個步驟:

工作人員需要對用戶提出的功能要求進行分析理解,做出電路系統的整體規劃,形成詳細的技術指標,確定初步方案。例如,要設計一個電子屏,需要考慮供電方式、工作頻率、產品體積、成本、功耗等,電路實現采用 ASIC 還是選用 FPGA/CPLD 器件等。

正確地分析了用戶的電路需求后,就可以進行邏輯功能的總體設計,設計整個電路的功能、接口和總體結構,考慮功能模塊的劃分和設計思路,各子模塊的接口和時序(包括接口時序和內部信號的時序)等,向項目組成員合理分配子模塊設計任務。

可以用任意的文本編輯器,也可以用專用的 HDL 編輯環境,對所需求的數字電路進行設計建模,保存為 .v 文件。

對建模文件進行編譯,對模型電路進行功能上的仿真驗證,查找設計的錯誤并修正。

此時的仿真驗證并沒有考慮到信號的延遲等一些 timing 因素,只是驗證邏輯上的正確性。

綜合(synthesize),就是在標準單元庫和特定的設計約束的基礎上,將設計的高層次描述(Verilog 建模)轉換為門級網表的過程。邏輯綜合的目的是產生物理電路門級結構,并在邏輯、時序上進行一定程度的優化,尋求邏輯、面積、功耗的平衡,增強電路的可測試性。

但不是所有的 Verilog 語句都是可以綜合成邏輯單元的,例如時延語句。

根據邏輯綜合出的網表與約束文件,利用廠家提供的各種基本標準單元庫,對門級電路進行布局布線。至此,已經將 Verilog 設計的數字電路,設計成由標準單元庫組成的數字電路。

布局布線后,電路模型中已經包含了時延信息。利用在布局布線中獲得的精確參數,用仿真軟件驗證電路的時序。單元器件的不同、布局布線方案都會給電路的時序造成影響,嚴重時會出現錯誤。出錯后可能就需要重新修改 RTL(寄存器傳輸級描述,即 Verilog 初版描述),重復后面的步驟。這樣的過程可能反復多次,直至錯誤完全排除。

完成上面所有步驟后,就可以通過開發工具將設計的數字電路目標文件下載到 FPGA/CPLD 芯片中,然后在電路板上進行調試、驗證。

如果要在 ASIC 上實現,則需要制造芯片。一般芯片制造時,也需要先在 FPGA 板卡上進行邏輯功能的驗證。

到此,關于“Verilog設計方法及流程是什么”的學習就結束了,希望能夠解決大家的疑惑。理論與實踐的搭配能更好的幫助大家學習,快去試試吧!若想繼續學習更多相關知識,請繼續關注億速云網站,小編會繼續努力為大家帶來更多實用的文章!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。