您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

EXOSTIV波形調試器為FPGA提供創新型調試的實例分析,相信很多沒有經驗的人對此束手無策,為此本文總結了問題出現的原因和解決方法,通過這篇文章希望你能解決這個問題。

FPGA調試是電子系統設計中不可或缺的重要環節,流程涉及多種技術、工具,而工程師的關鍵工作在于選擇正確的技術以更高效實現項目目標。隨著FPGA設計的功能趨于復雜,規模逐漸變大,傳統的調試手段有著透視性差,無法調試內部信號,調試速度慢等缺陷,已無法滿足現階段的需求,因此尋找一種更為高效適配的調試手段成為了FPGA開發者們的迫切需求。

EXOSTIV波形調試器。它提供類似模擬器的可見性 - 比基于JTAG的工具高出200,000倍 - 為標準和定制的FPGA板快速調試周轉時間。

EXOSTIV調試系統部件

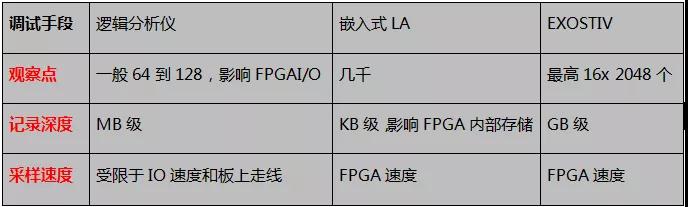

對比傳統調試手段

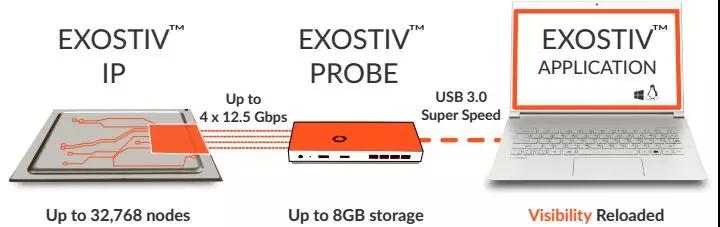

EXOSTIV波形調試器可提升FPGA可視性20萬倍,它利用FPGA芯片的多個Gbit收發接口將記錄的波形數據存儲到FPGA外的設備中,其數據收集并不占用FPGA芯片本身的資源。該波形調試器目前最大可以存儲8GB的調試數據,支持同時持續記錄32768個內部信號,硬件加速測試工具讀取和顯示大規模的數字和模擬波形數據。

· Xilinx版支持Zynq、7系列和UltraScale(+)系列

· Intel版本支持10系列 Cyclone V和Stratix V系列

· 需要使用FPGA廠商軟件對IP進行綜合

· 最高4x12.5 Gbps MGT 連接

· MYRIAD波形查看器(TB級)

EXOSTIV 調試系統

EXOSTIV Probe 和連接線

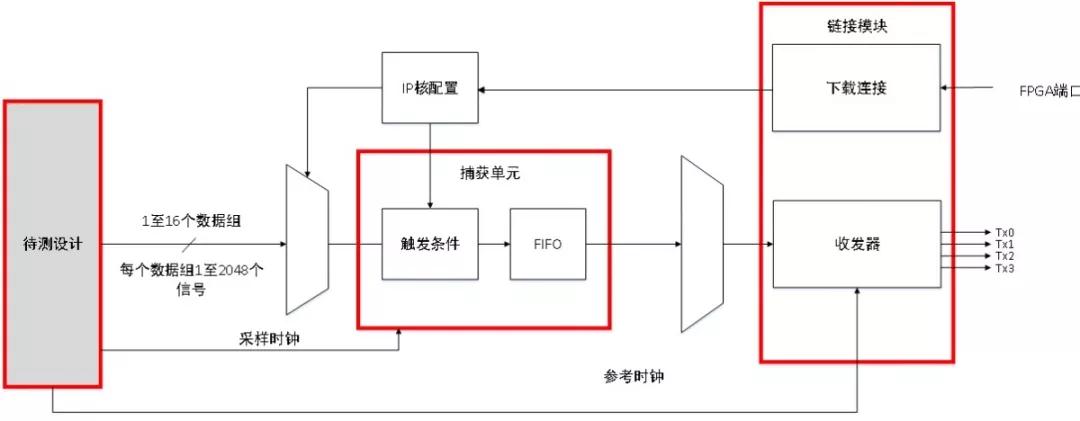

· 建立IP核與調試器的鏈接:可設置芯片類型,

鏈接方式 (HDMI或SFP)等;

· 設置捕獲單元:配置需要采集的信號及其觸發

條件;

· 生成IP核并注入至設計:根據前兩步的配置會

生成IP核,調試器會將IP核注入設計,根據IP

核中的設置開始捕獲信號;

· 配置條件并運行:完成IP核生成后,用戶依然

可以對捕獲單元進行一部分的修改, 例如觸發

條件,觸發位置等;

· 讀取圖像并調試:采集后的數據通過高速串口

存儲到 Probe中,在波形調試界面可查看并存

儲波形。

EXOSTIV工作原理圖

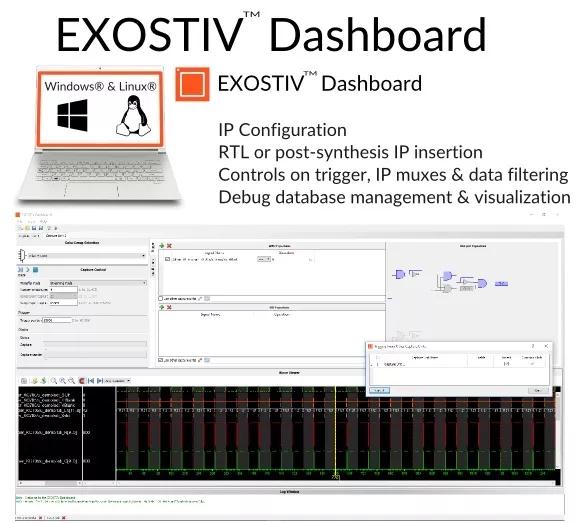

波形調試界面

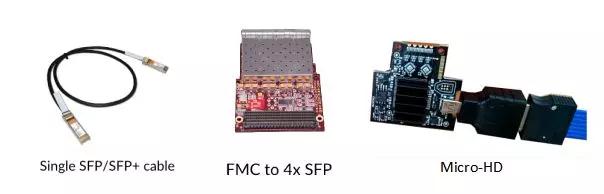

· SFP/SFP+/QSFP/QSP+接口;

· HDMI接口,或Micro-HDMI連接器;

· 連接到FMC,可使用FMC to HDMI、FMC to

SFP/QSFP模塊適配器。

支持芯片及平臺

我們看到現在很多新興行業,比如云計算、5G通信、人工智能(AI)、機器學習、自動駕駛等應用場景都需要強大的計算能力來支持,因此FPGA正大量被使用在各個領域,在設計趨于復雜的同時,它們也占用了更多的邏輯資源,信號量也呈現指數級別的增加,EXOSTIV 的出現提供了更強大的信號可視化能力,毫無疑問的方便了電子工程師們的調試工作,更快的將FPGA設計方案交付。

看完上述內容,你們掌握EXOSTIV波形調試器為FPGA提供創新型調試的實例分析的方法了嗎?如果還想學到更多技能或想了解更多相關內容,歡迎關注億速云行業資訊頻道,感謝各位的閱讀!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。