您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇文章給大家分享的是有關FIFO IP核使用的注意事項有哪些,小編覺得挺實用的,因此分享給大家學習,希望大家閱讀完這篇文章后可以有所收獲,話不多說,跟著小編一起來看看吧。

FIFO?還是FIFO IP核?這也需要寫總結嗎?太容易了吧。如果我是一個正在處于面試找工作中的年輕人,肯定關注的是如何手撕FIFO,這也是當時校招時候干過的事情。但是作為一個FPGA工程師,我們更常使用的是FIFO的IP核,或者必然使用的是FIFO IP核,簡單快捷優化。使用FIFO IP核的時候,或者設計電路使用FIFO IP的時候,對于新手或者不是精通的情況下,個人建議一點是對自己定制的FIFO仿真一下(或者嚴格遵守數據手冊),做到時序關系清晰后,再設計電路。注意:不要不屑于此!

下面講解幾點關于FIFO IP核使用時的注意事項,想到哪里到哪里!

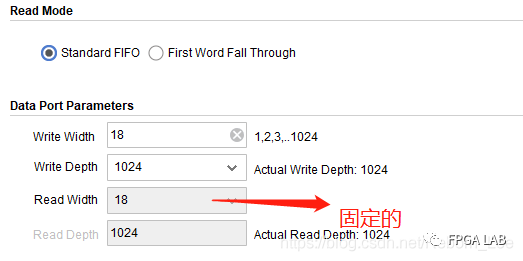

FIFO定制頁面存在一個Enable Safety Circuit,如下:

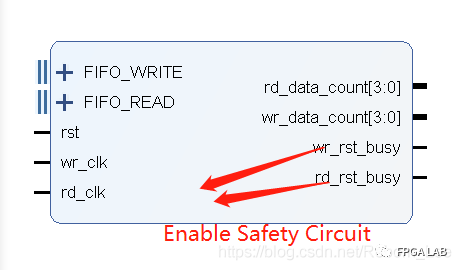

選擇此選項,存在兩個額外輸出信號:

選擇此選項,存在兩個額外輸出信號:

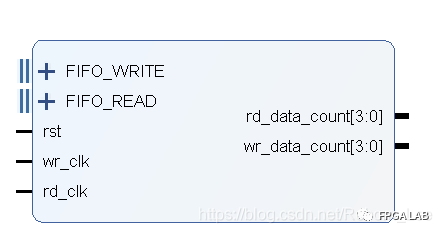

如果不選擇Enable Safety Circuit,則不存在這兩個信號輸出:

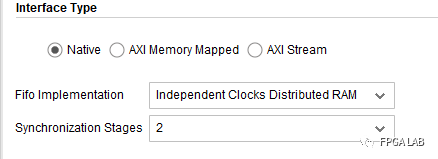

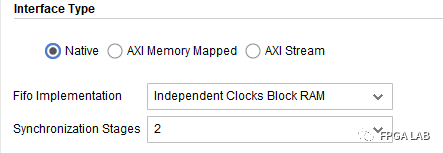

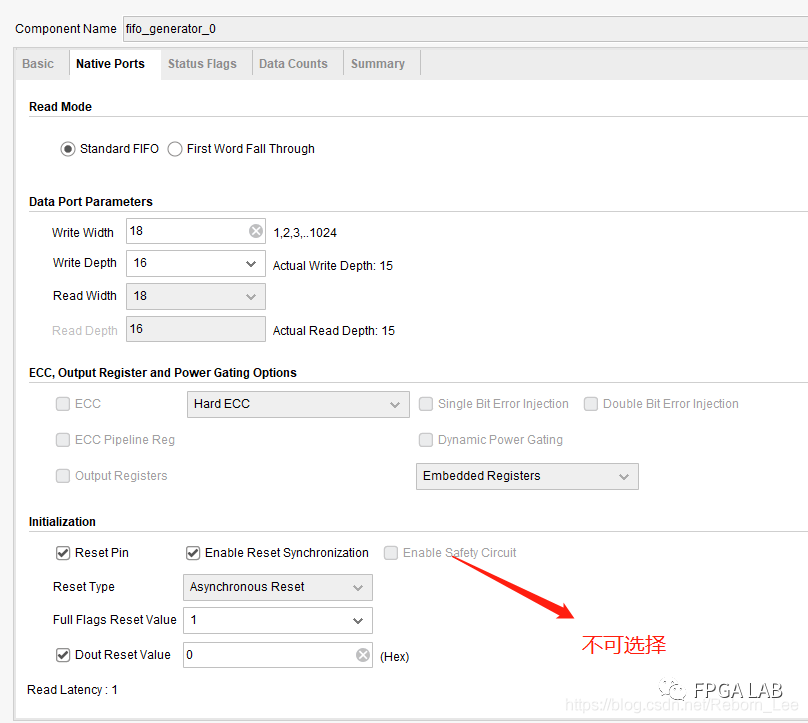

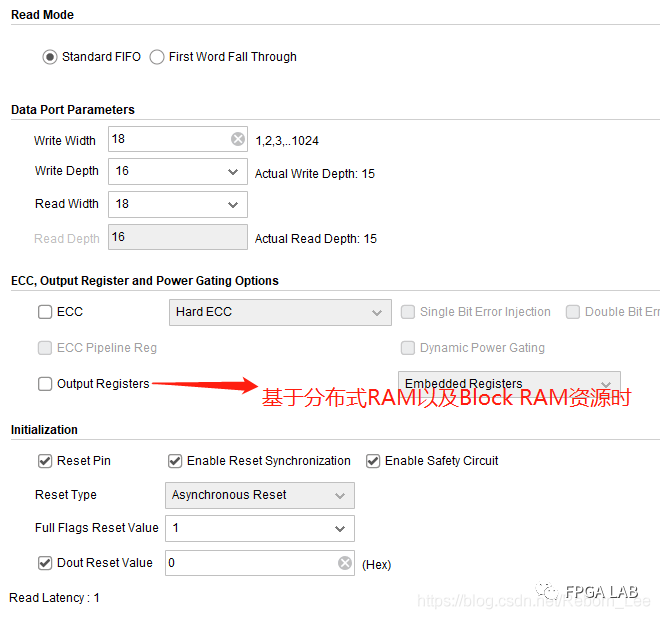

此選項僅僅針對基于Bram資源的FIFO定制,如果使用分布式RAM資源,則不可選擇:

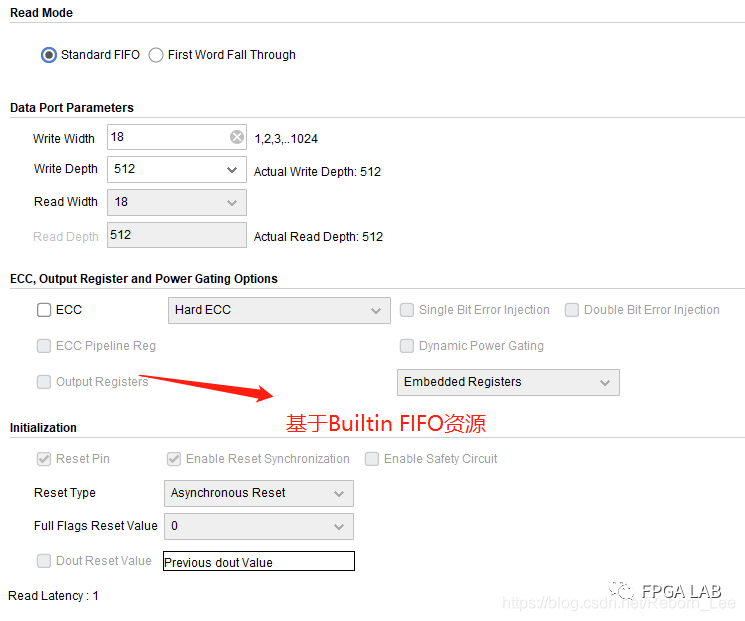

同理Builtin FIFO資源的FIFO也不可選擇。

假如使用的是此Block RAM資源的FIFO,選擇此信號,有什么作用呢?多出來的兩個信號是什么意思?有什么用途?筆者曾在仿真中犯過一個錯誤,就是在復位后的幾個時鐘直接給寫使能,可是怎么寫也寫不進去數據,后來發現是wr_rst_busy處于高電平狀態,自然是不能寫的。所以判斷寫使能有效,可以將此信號作為判斷條件之一,如果該信號為高,則不能寫入。

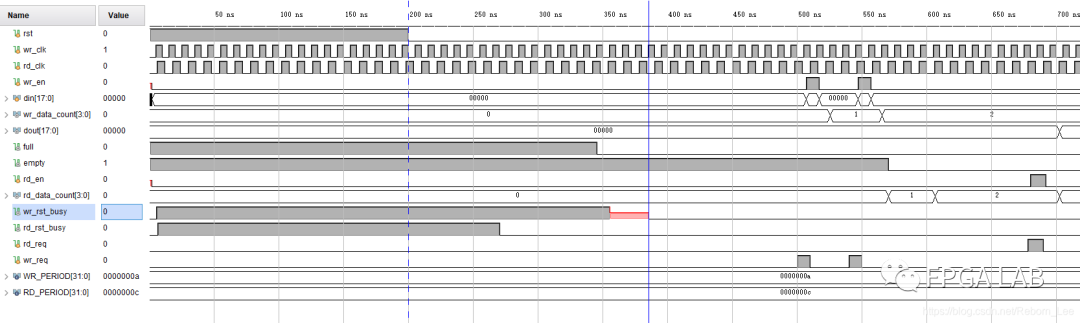

這就引發一個疑問?既然存在這樣一個問題,那么多久之后才能對FIFO寫入數據呢?那就要看復位無效之后多久這個信號才能被拉低,且仿真看看: 可見,大概20多個時鐘周期之后,這個信號就拉低無效了。這樣會不會對我們使用FIFO有影響呢?可以想象下20多個時鐘才多長時間,周期ns級別,況且寫使能可以以此信號作為寫使能有效條件,因此可以很容易規避這個問題,這里列出來的原因就是為了仿真時候,如果遇到了寫不進去的情況時,考慮下這個問題,以免莫名其妙,百思不得其解。

可見,大概20多個時鐘周期之后,這個信號就拉低無效了。這樣會不會對我們使用FIFO有影響呢?可以想象下20多個時鐘才多長時間,周期ns級別,況且寫使能可以以此信號作為寫使能有效條件,因此可以很容易規避這個問題,這里列出來的原因就是為了仿真時候,如果遇到了寫不進去的情況時,考慮下這個問題,以免莫名其妙,百思不得其解。

Xilinx對安全電路的使用還有一條建議,就是選擇異步復位時,有可能導致BRAM數據的損壞,此時推薦使用安全電路。

對于異步FIFO而言,好像也只能使用異步復位,這就更有必要性了。

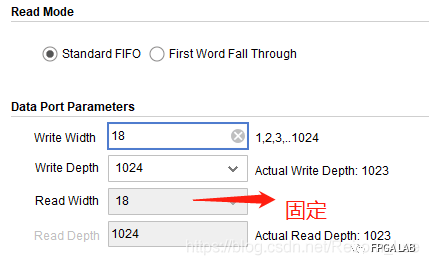

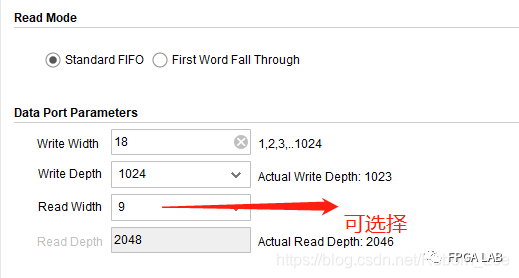

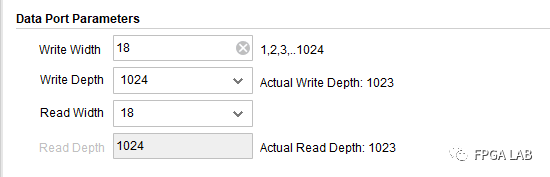

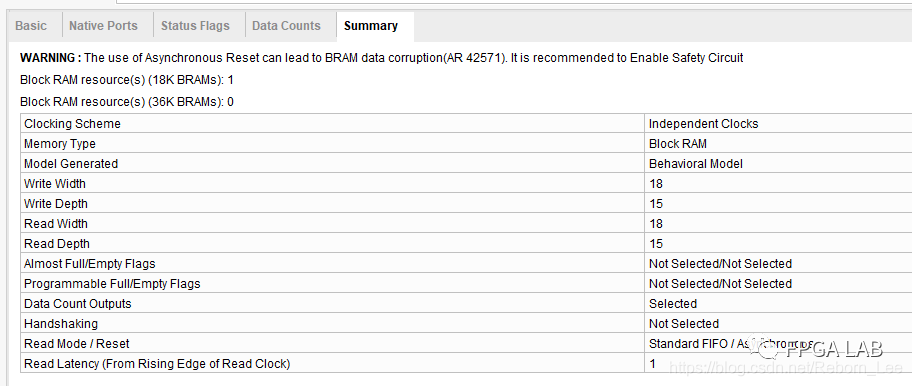

定制FIFO消耗資源與使用什么資源生成FIFO有關,對于Block RAM資源的FIFO使用的自然是Block RAM資源,7系列的用于生成FIFO的Block RAM資源大小有兩種,18Kbit以及36Kbit兩種,一般默認bit,可以說是18K以及36K。

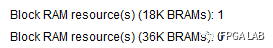

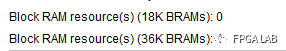

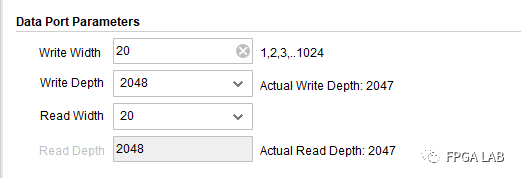

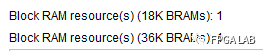

FIFO位寬乘深度小于18K,自然是使用了一個18K的Bram,如下:

使用Block RAM資源:

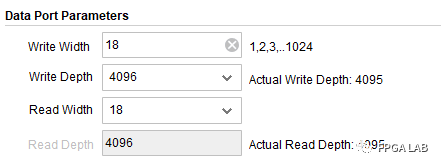

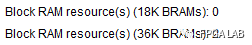

大于18K的自然是一個36KBlock RAM:

使用BRAM資源:

大于36K,情況多變,是18K以及36K的組合:

使用分布式RAM資源以及Block RAM資源的FIFO可以選擇輸出寄存器打拍一次,這樣自然Read Latency為2,使用Builtin FIFO資源無法選擇輸出寄存器打拍。

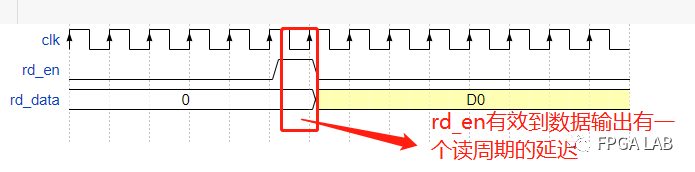

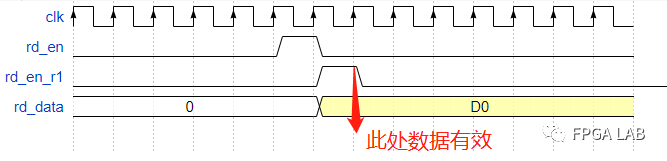

假如都不寄存器輸出,即輸出不寄存一拍,那么這里的Read Latency = 1具體是什么含義呢?我想時序圖最能說明一切:

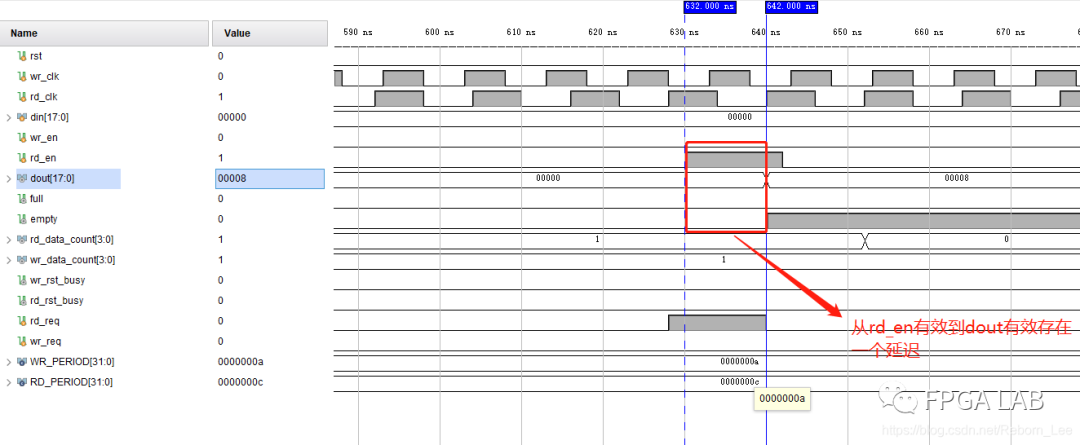

實際仿真看一下:FIFO IP生成總結:

因此如果需要使用rd_data數據的話,需要對讀使能延遲一拍,判斷rd_en_r1有效時使用讀數據的實際值:

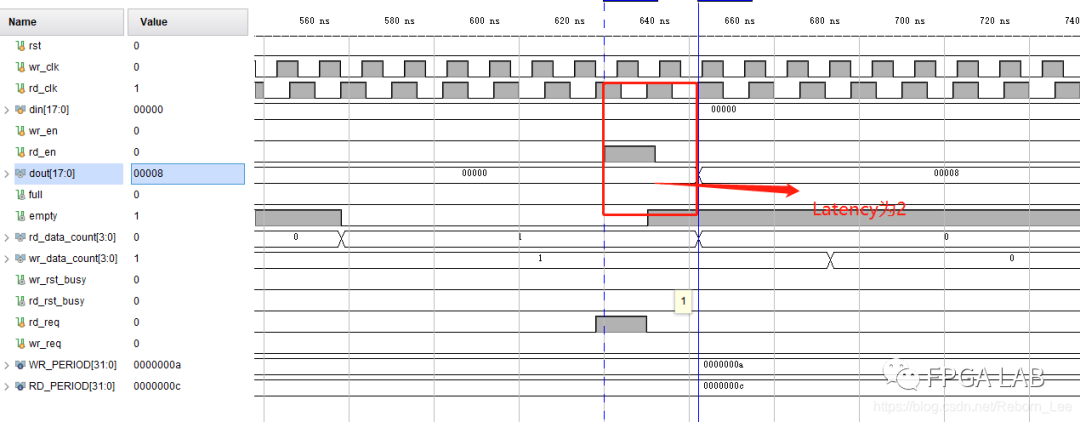

知道了Read Latency為1的含義,為2的情況自然很容易理解,在添加了寄存器輸出的時候,就會使得Read Latency為2,如下:

同樣仿真實現下:

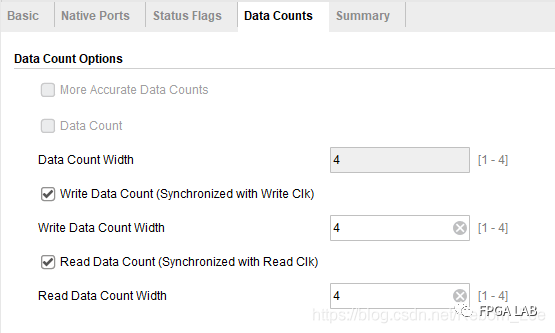

在FIFO定制頁面有如下選擇:Write Data Count,Read Data Count這兩個選擇,是什么意思呢?

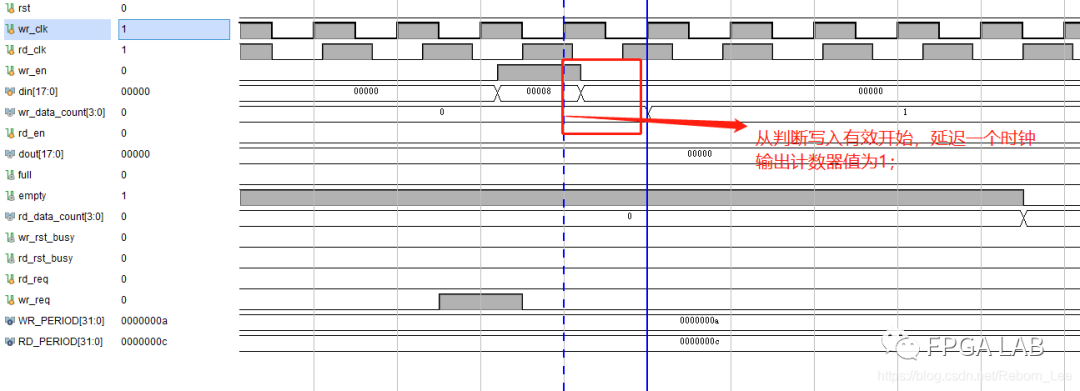

那我們寫進去一個數據,看看兩者數據的變化:

從寫計數有效開始,延遲一個時鐘,計數器值更新為1,意思就是寫入了一個數據;注意:我們在實際使用FIFO輸出參數之前,一定要仿真看下時序關系,以防用錯。

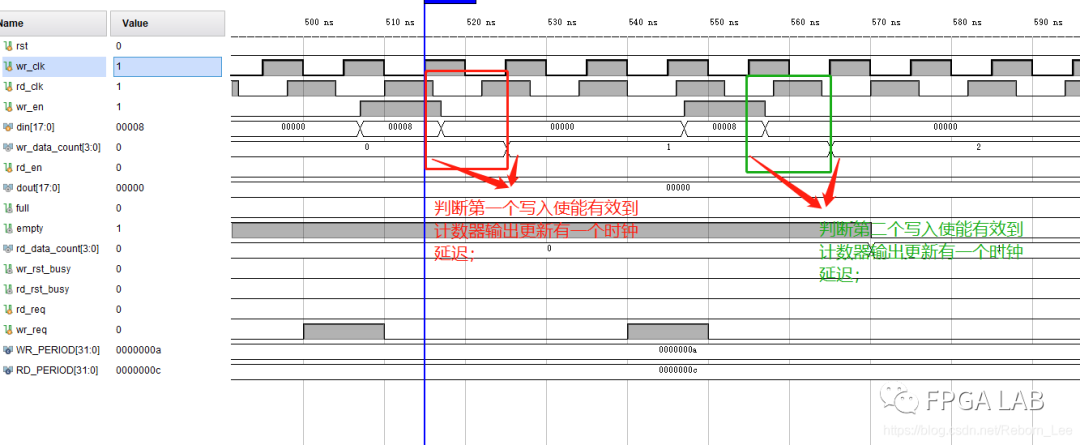

我們嘗試寫入兩個數據,來驗證下這種關系:

關系一致。

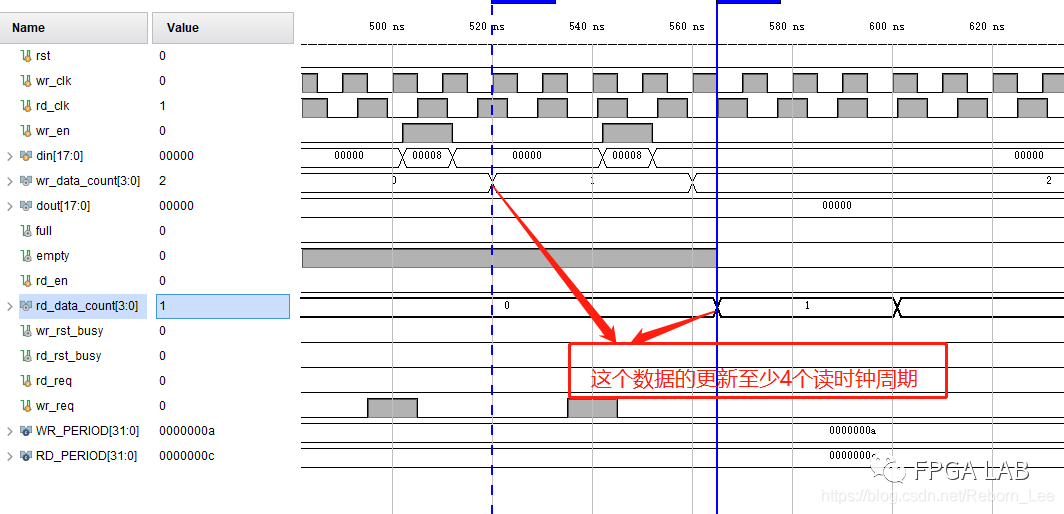

讀計數器的含義是FIFO內部存放了多少數據?但這個數據的更新需要一定的時間,例如:

數據的更新需要至少4個讀時鐘周期,因此,這個數據我們不能寫入之后立即使用;這個延遲是異步FIFO內部跨時鐘域的結果。

注意:使用FIFO IP核內部輸出信號的時候,保險起見,需要自己仿真下,認識下時序關系后再設計電路。

例如寫入了兩個數據,之后又讀出了一個,那這個值最終一定是1;

仿真驗證了這個結果。

上面說了這些情況,其實都在數據手冊中有體現,但是對于一個FIFO,大家都傾向于直接使用,不屑于看數據手冊,不得不說,這都是年輕氣盛的表現,或者天賦異稟。

因此,對于這種情況,我們有兩個選擇:一是看數據手冊;二是自己仿真自己定制的IP核,看清時序后設計電路。

以上就是FIFO IP核使用的注意事項有哪些,小編相信有部分知識點可能是我們日常工作會見到或用到的。希望你能通過這篇文章學到更多知識。更多詳情敬請關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。