您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇內容主要講解“SDRAM是什么”,感興趣的朋友不妨來看看。本文介紹的方法操作簡單快捷,實用性強。下面就讓小編來帶大家學習“SDRAM是什么”吧!

Synchronous Dynamic Random Access Memory: 同步動態隨機存儲器. 同步 : 由soc發送時鐘給SDRAM, 通過該時鐘的節拍來發送控制信號. 動態 : 存儲器需要不斷的刷新來保證數據不丟失. 隨機 : 數據非線性存儲, 可自由指定地址進行數據的讀寫

圖1 本開發板用兩片sdram來配置為32bit位寬的sdram.

sdram的檢索原理和表格一樣, 通過先指定行, 再指定列就能準確找到所需要的存儲單元. 但是由于技術/成本的原因, 一個sdram內部不可能只有一個表格, 目前基本是4個, 這個類似表格一樣的結構叫做 邏輯Bank, L-Bank. 這樣要找到某個存儲單元就要先確定是哪個bank, 然后選定行,再選定列.

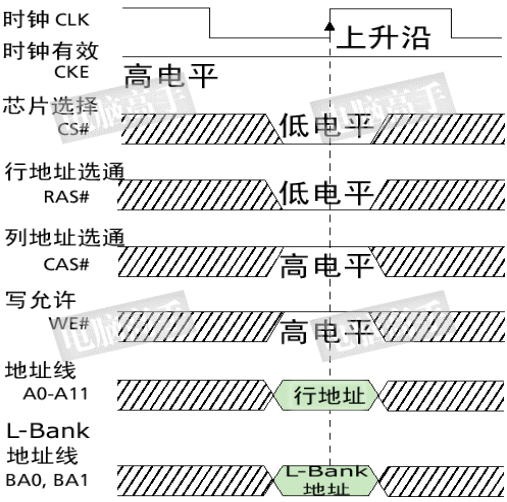

行有效

必須先使能芯片, 選中相應的L-BANK, 再使能 行(ROW), 再使能 列(COLUMN)來對某個存儲單元進行讀寫.

圖2 行有效時序圖

通過BA0\BA1來選中某個L-BANK, 通過RAS\CAS來區分 行 與 列. 這是同時進行的, 所以行有效也可以稱為 L-BANK有效

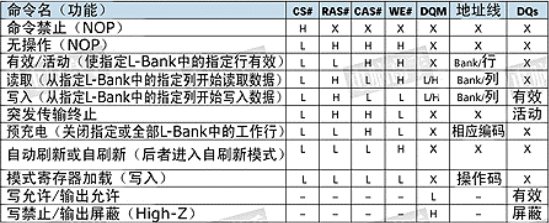

列讀寫

行選通之后就可以發送列地址對存儲單元進行讀寫了. 讀/寫 命令是通過 WE 信號線來區分的, WE = 1 : 寫入 ; WE = 0 : 讀取

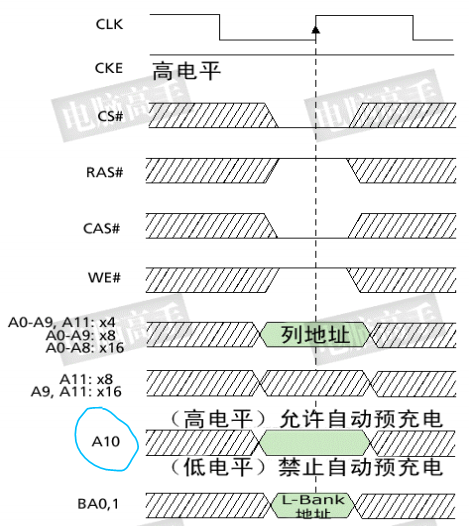

圖3 命令列表

由上表可知, SDRAM的各種指令都是通過 控制/地址線 的高低電平組合來完成的, 并沒有命令字. 所以 讀寫命令 與 列地址 同時發出.

圖4 讀寫操作示意圖

CAS(ColumnAddress Strobe,列地址選通脈沖)信號配合A0-A9/A11(不固定)來確定具體的列地址.

圖5

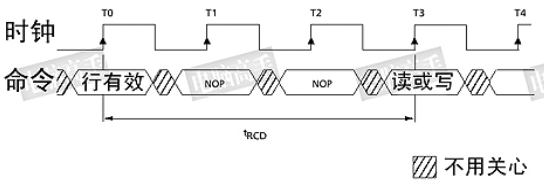

在發送列讀寫命令時必須要與行有效命令有一個間隔,這個間隔被定義為tRCD,即RAS to CAS Delay(RAS至CAS延遲),也可以理解為行選通周期,這應該是根據芯片存儲陣列電子元件響應時間(從一種狀態到另一 種狀態變化的過程)所制定的延遲。tRCD是SDRAM的一個重要時序參數,廣義的tRCD以時鐘周期(tCK,Clock Time)數為單位,比如tRCD=2,就代表延遲周期為兩個時鐘周期,具體到確切的時間,則要根據時鐘頻率而定,對于PC100的SDRAM,tRCD=2,代表20ns的延遲,對于PC133則為15ns

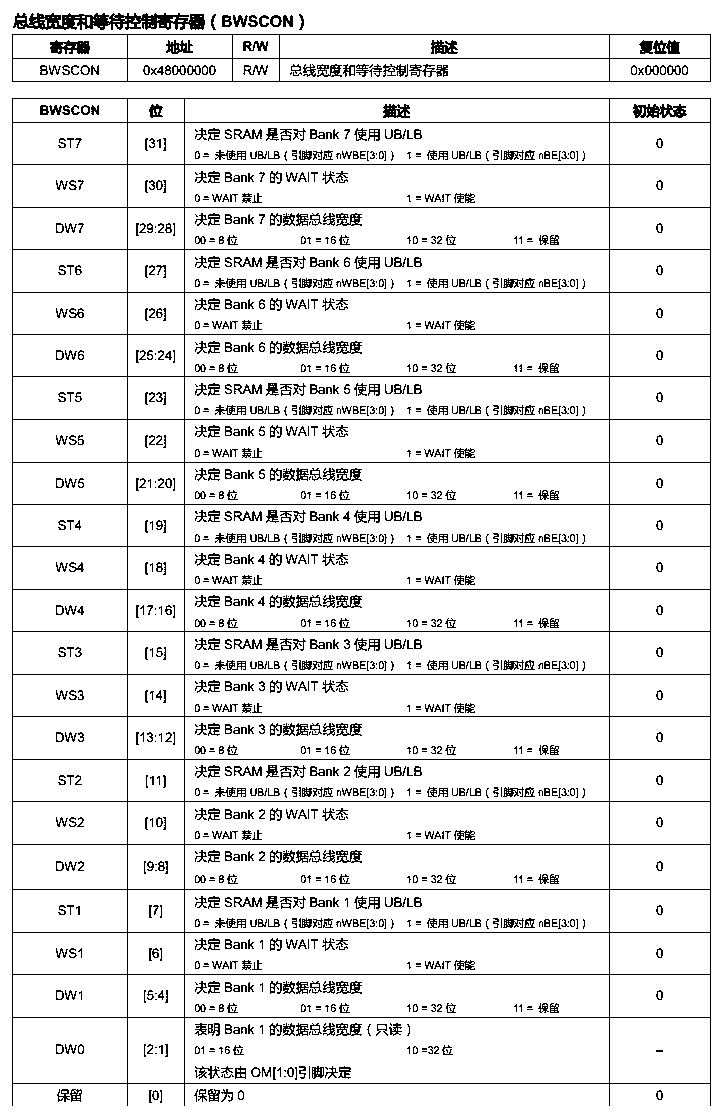

BWSCON = 0x2201 1110

BWSCON[31] = 0, 禁止數據掩碼引腳

數據掩碼

在講述讀/寫操作時,我們談到了突發長度。如果BL=4,一次就傳送4×64bit的數據。但是,如果第二筆 數據是不需要的,怎么辦?為了屏蔽不需要的數據,人們采用了數據掩碼(Data I/O Mask,簡稱DQM)技術。通過DQM,內存可以控制I/O端口取消哪些輸出或輸入的數據。這里需要強調的是,在讀取時,被屏 蔽的數據仍然會從存儲體傳出,只是在“掩碼邏輯單元”處被屏蔽。為了精確屏蔽一個P-Bank位寬中的每個字節,每個DIMM有8個DQM信號線,每個信號針對一個字節。這樣,對于4bit位寬芯片,兩個芯片共用一個DQM信號線,對于8bit位寬芯片,一個芯片占用一個DQM信號,而對于16bit位寬芯片,則需要兩個DQM引腳。SDRAM官方規定,在讀取時DQM發出兩個時鐘周期后生效,而在寫入時,DQM與寫入命令一樣是立即成效

BWSCON[30] = 0, 禁止WAIT信號

BWSCON[29:28] = 1:0; 設置BANK7數據總線寬度為32bit

(BANK6同BANK7)

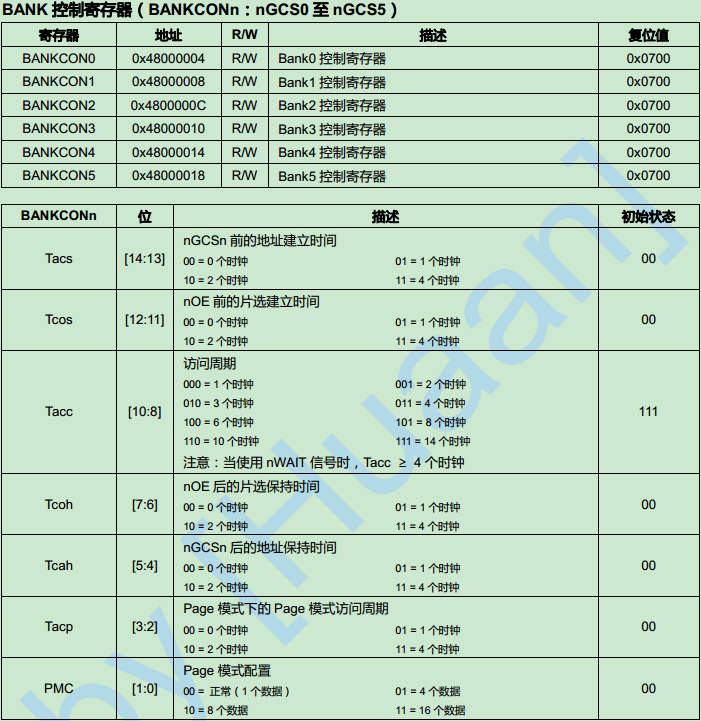

BANKCONx = 0x0700

BANKCONx( 0 <= x <= 5)用來控制BANK0~BANK5外接設備的訪問時序, 采用默認值即可

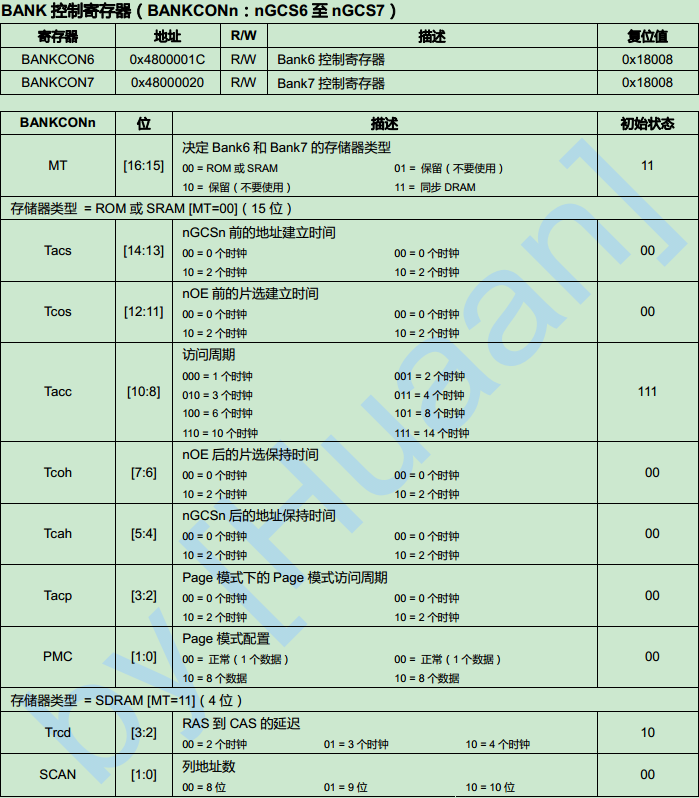

BANKCONx(6 <= x <= 7) = 0x0001 8005

BANKCONx[16:15] = 1:1, 設置存儲器類型為 SDRAM

BANKCONx[3:0] = 0:1:0:1, 設置RAS到CAS的延遲(tRCD)為3個時鐘, 設置列地址數為9bit

REFRESH = 0x008C 07A3

BANKCONx[23] = 1, 使能自動刷新功能

BANKCONx[22] = 0, Auto refresh, 等于1為 self refresh

BANKCONx[21:20] = 0:0, 預充電時間為2個時鐘周期 (預充電見解釋)

BANKCONx[19:18] = 1:1, 設置半行周期時間為7個時鐘

BANKCONx[10:0] 設置刷新計數, 刷新計數= 2^11+1-12*7.8=1955( 0x07A3 )

刷新

之所以稱為DRAM,就是因為它要不斷進行刷新(Refresh)才能保留住數據,那么要隔多長時間進行一次刷新呢? 我們在看內存規格時,經常會看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的標識,這里的4096與8192就代表這個芯片中每個L-Bank的行數。刷新命令一次對一行有效,發送間隔也是隨總行數而變化,4096行時為15.625μs(微秒,1/1000毫秒),8192行時就為7.8125μs. 刷新操作分為兩種:Auto Refresh,簡稱AR與Self Refresh,簡稱SR。不論是何種刷新方式,都不需要外部提供行地址信息,因為這是一個內部的自動操作。

預充電

由于SDRAM的尋址具有獨占性,所以在進行完讀寫操作后,如果要對同一L-Bank的另一行進行尋址,就要將原來有效(工作) 的行關閉,重新發送 行/列地址。L-Bank關閉現有工作行,準備打開新行的操作就是預充電(Precharge)

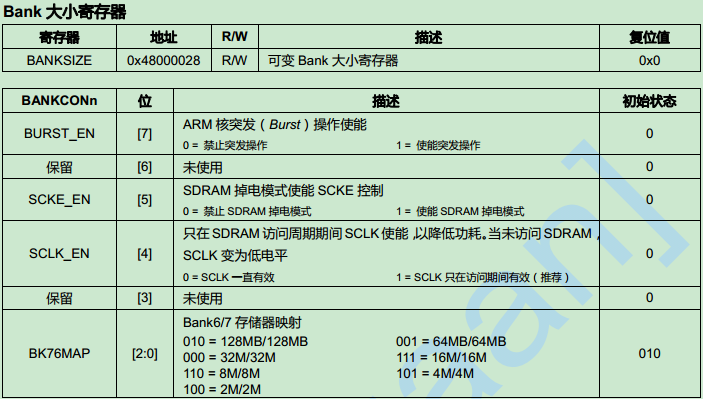

BANKSIZE = 0xB1

BANKCONx[7] = 1, 使能突發操作

BANKCONx[6] = 0, 保留

BANKCONx[5] = 1, 使能SDRAM掉電模式

BANKCONx[4] = 1, 設置只在訪問SDRAM的時候發送時鐘

BANKCONx[3] = 0, 保留

BANKCONx[2:0] = 0:0:1, BANK6/BANK7存儲器映射大小 = 64MB/64MB

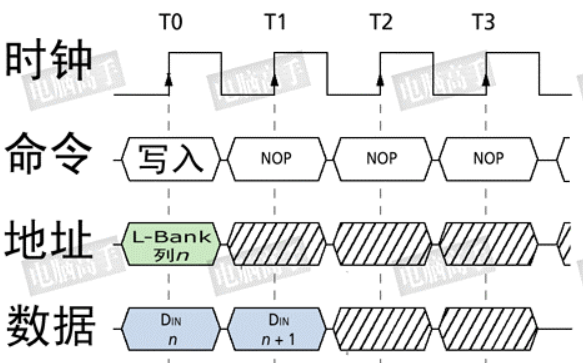

數據輸入(寫入)

圖7

數據寫入的操作也是在tRCD之后進行,但此時沒有了CL(記住,CL只出現在讀取操作中),行尋址與列尋址的時序圖和上文一樣 ,只是在列尋址時,WE#為有效狀態。從圖中可見,由于數據信號由控制端發出,輸入時芯片無需做任何調校,只需直接傳到數據輸入寄存器中,然后再由寫入驅動器進行對存儲電容的充電操作,因此數據可以與CAS同時發送,也就是說寫入延遲為0。不過,數據并不是即時地寫入存儲電容,因為選通三極管 (就如讀取時一樣)與電容的充電必須要有一段時間,所以數據的真正寫入需要一定的周期。為了保證數據的可靠寫入,都會留出足夠的 寫入/校正時間(tWR,Write Recovery Time),這個操作也被稱作寫回(Write Back)。tWR至少占用一個時鐘周期或再多一點(時鐘頻率越高,tWR占用周期越多),有關它的影響將在下文進一步講述

突發長度

突發(Burst)是指在同一行中相鄰的存儲單元連續進行數據傳輸的方式,連續傳輸所涉及到存儲單元(列)的數量就是突發長度(Burst Lengths,簡稱BL)

非突發連續讀取模式:依次單獨尋址,此時可等效于BL=1。雖然可以讓數據是連續的傳輸,但每次都要發送列地 址與命令信息,控制資源占用極大

突發連續讀取模式:只要指定起始列地址與突發長度,尋址操作與數據的讀取操作自動進行,只要控制好兩段突發讀取命令的間隔周期(與BL 相同)即可做到連續的突發傳輸

突發讀/突發寫,表示讀與寫操作 都是突發傳輸的,每次讀/寫操作持續BL所設定的長度,這也是常規的設定

突發讀/單一寫,表示讀操作是突發傳輸,寫操作則只是 一個個單獨進行。突發傳輸模式代表著突發周期內所涉及到的存儲單元的傳輸順序

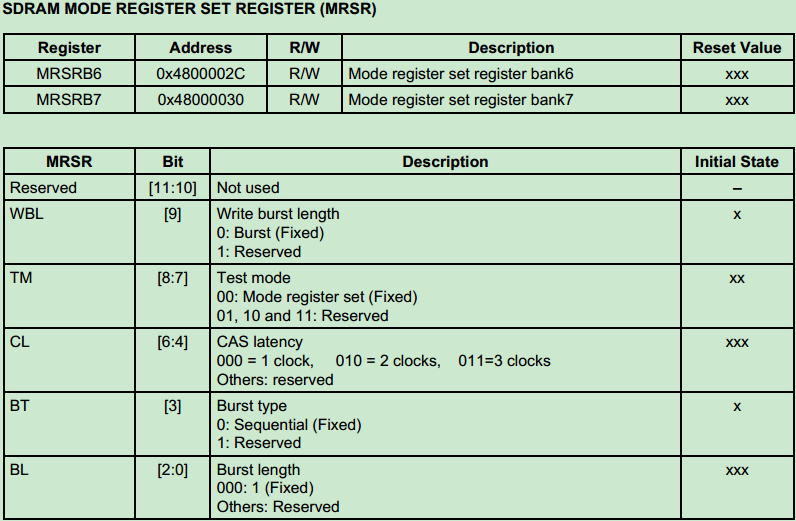

MRSR = 0x30

MRSR[6:4] = 0:1:1, 設置 發送讀取命令到第一個數據輸出的時間 為 3 個時鐘周期

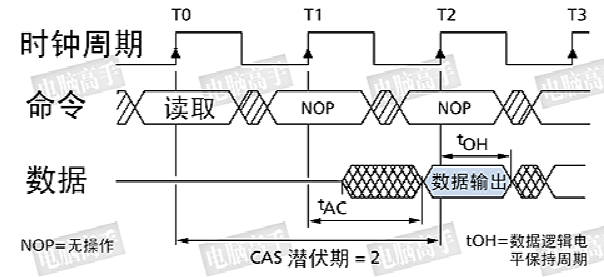

數據輸出(讀出)

在CAS 發出之后,仍要經過一定的時間才能有數據輸出,從CAS與讀取命令發出到第一筆數據輸出的這段時間,被定義為CL(CAS Latency,CAS潛伏期)。由于CL只在讀取時出現,所以CL又被稱為讀取潛伏期(RL,Read Latency)。CL的單位與tRCD一樣,為時鐘周期數,具體耗時由時鐘頻率決定

圖6 CL=2與tAC示意圖

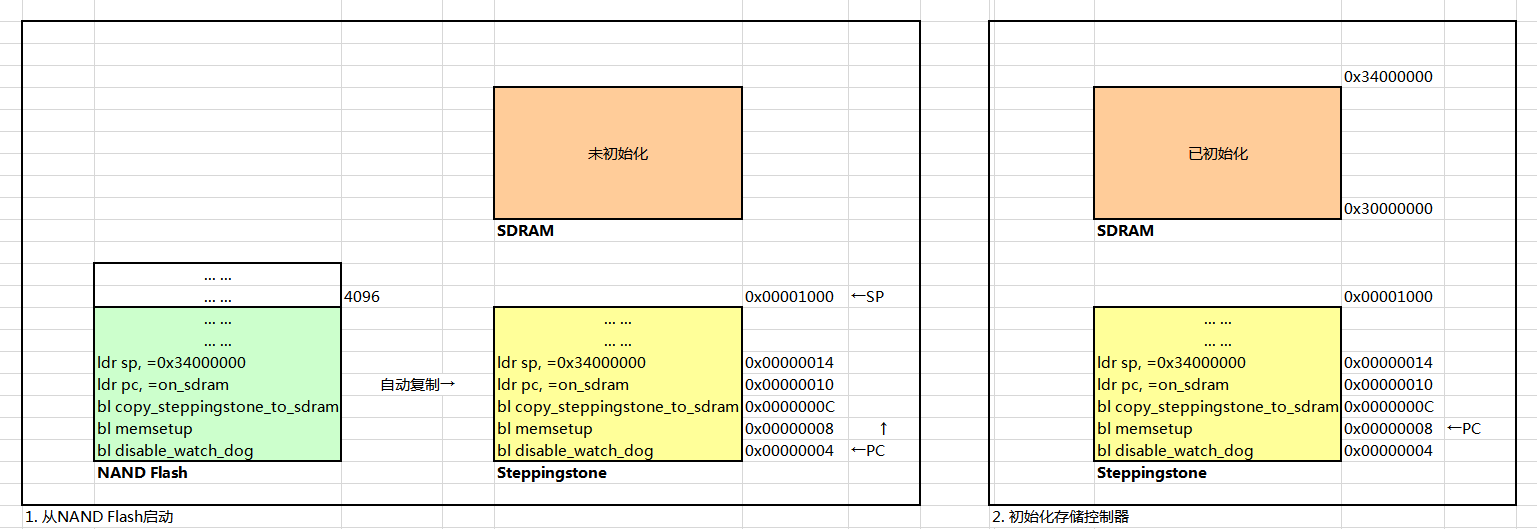

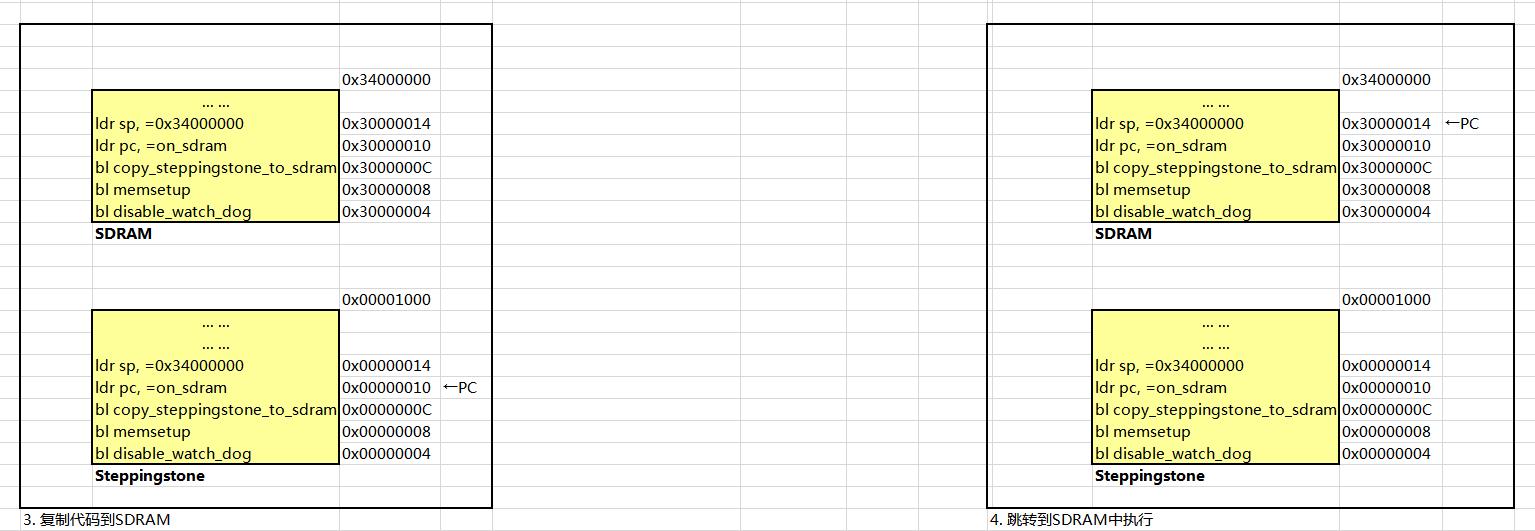

JZ2440的裸機SDRAM代碼執行流程:

到此,相信大家對“SDRAM是什么”有了更深的了解,不妨來實際操作一番吧!這里是億速云網站,更多相關內容可以進入相關頻道進行查詢,關注我們,繼續學習!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。