您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

怎么在RTL級別電路建模優化congestion問題,針對這個問題,這篇文章詳細介紹了相對應的分析和解答,希望可以幫助更多想解決這個問題的小伙伴找到更簡單易行的方法。

數字IC設計可謂環環相扣,很多環節都存在迭代發生的可能。

在最初芯片設計之前主要考慮PPA,即power、performance和area,但是實際項目中還存在仿真、測試及后端實現的問題。

下面主要介紹RTL設計引入的后端實現過程中的布線(routing)問題。

后端物理實現需要完成芯片中布局布線(place&routing)的工作。在物理實現過程中routing之前的floorplan階段、placement階段和CTS階段都對routing效果有很大的影響,也有很多針對congestion的優化技術。

但是,實際項目中依然存在走線無法繞通的問題,可能是因為芯片對利用率要求可能比較苛刻,也可能是因為在RTL級別建模電路時造成了難繞線問題。

芯片物理實現中的macro走線、電源布線等占據走線資源,時序和串擾也會給走線引入更多的問題,我們應該盡量減少由RTL級別電路建模引入的無法走線問題。

下面舉兩個在RTL級別優化電路走線問題的示例:

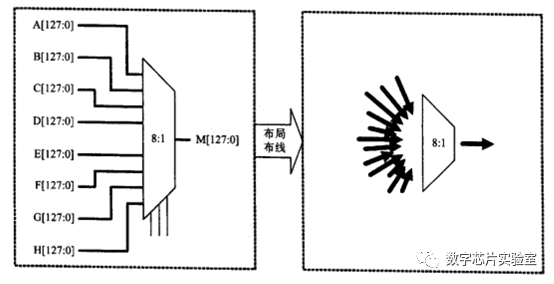

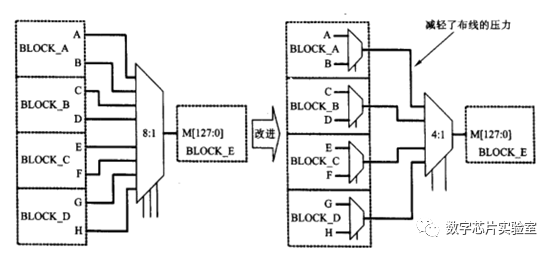

1、大扇入

reg [2:0] SEL ;reg [127:0] A,B,C,D,E,F,G,H, SEL;always@(*) begin case(SEL) 2’b000:M <= A ; 2’b001:M <= B; 2’b010:M <= C ; 2’b011:M <=D ; 2’b100:M <= E ; 2’b101:M <= F ; 2’b110:M <= G ; 2’b111:M <= H ;endcaseend

在上面的電路中一個MUX電路具有非常大的扇入(8X128=1024)。可以通過級聯MUX優化走線問題:

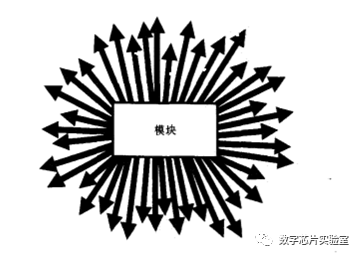

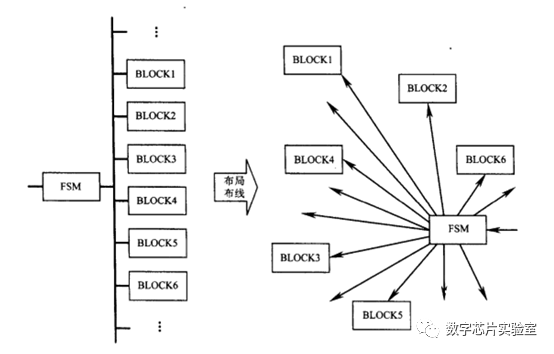

2、大扇出

設計中還存在一種被廣泛使用的信號,這種信號具有非常大的扇出,例如時鐘、復位和使能等。

為了解決這個問題,可以復制信號源。這也體現了利于走線和硬件開銷之間的折中。

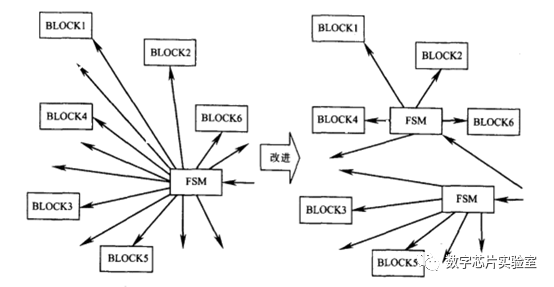

上面這個有限狀態機輸出信號被多個模塊使用,可以復制這個狀態機,優化走線問題。

關于怎么在RTL級別電路建模優化congestion問題問題的解答就分享到這里了,希望以上內容可以對大家有一定的幫助,如果你還有很多疑惑沒有解開,可以關注億速云行業資訊頻道了解更多相關知識。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。