您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這篇文章主要介紹STM32網絡中MII和RMII接口有什么用,文中介紹的非常詳細,具有一定的參考價值,感興趣的小伙伴們一定要看完!

SMI接口主要是用于和外部PHY芯片通信,配置PHY寄存器用的。

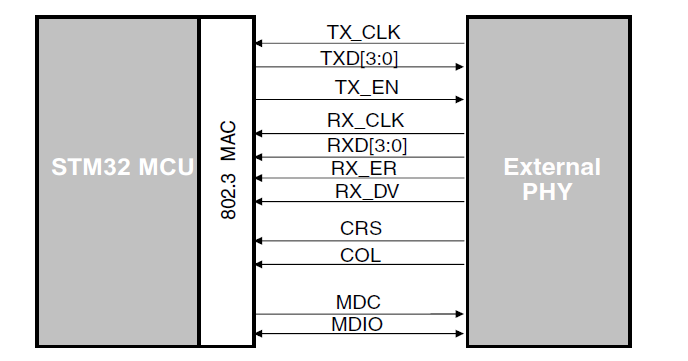

真正網絡通信的數據流并不是通過SMI接口傳輸的,是通過MII接口或者RMII通信的。

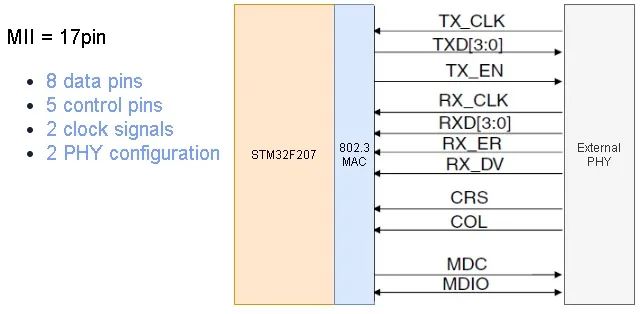

介質獨立接口(MII) 定義了10 Mbit/s 和100 Mbit/s 的數據傳輸速率下MAC 子層與PHY 之間的互連。

管腳定義介紹:

MII_TX_CLK:連續時鐘信號。該信號提供進行 TX 數據傳輸時的參考時序。標稱頻率為:速率為 10 Mbit/s 時為 2.5 MHz;速率為 100 Mbit/s 時為 25 MHz。

MII_TXD[3:0]:數據發送信號。該信號是 4 個一組的數據信號,由 MAC 子層同步驅動,在MII_TX_EN 信號有效時才為有效信號(有效數據)。MII_TXD[0] 為最低有效位,MII_TXD[3] 為最高有效位。禁止MII_TX_EN 時,發送數據不會對 PHY 產生任何影響。

MII_TX_EN:發送使能信號。該信號表示 MAC 當前正針對 MII 發送半字節。該信號必須與報頭的前半字節進行同步 (MII_TX_CLK),并在所有待發送的半字節均發送到 MII時必須保持同步。

MII_RX_CLK:連續時鐘信號。該信號提供進行 RX 數據傳輸時的參考時序。標稱頻率為:速率為 10 Mbit/s 時為 2.5 MHz;速率為 100 Mbit/s 時為 25 MHz。

MII_RXD[3:0]:數據接收信號。該信號是 4 個一組的數據信號,由 PHY 同步驅動,在MII_RX_DV 信號有效時才為有效信號(有效數據)。MII_RXD[0] 為最低有效位,MII_RXD[3] 為最高有效位。當 MII_RX_DV 禁止、MII_RX_ER 使能時,特定的MII_RXD[3:0] 值用于傳輸來自 PHY 的特定信息。

MII_RX_ER:接收錯誤信號。該信號必須保持一個或多個周期 (MII_RX_CLK),從而向MAC 子層指示在幀的某處檢測到錯誤。該錯誤條件必須通過 MII_RX_DV驗證。

MII_RX_DV:接收數據有效信號。該信號表示 PHY 當前正針對 MII 接收已恢復并解碼的半字節。該信號必須與恢復幀的頭半字節進行同步 (MII_RX_CLK),并且一直保持同步到恢復幀的最后半字節。該信號必須在最后半字節隨后的第一個時鐘周期之前禁止。為了正確地接收幀,MII_RX_DV 信號必須在時間范圍上涵蓋要接收的幀,其開始時間不得遲于 SFD 字段出現的時間。

MII_CRS:載波偵聽信號。當發送或接收介質處于非空閑狀態時,由 PHY 使能該信號。發送和接收介質均處于空閑狀態時,由 PHY 禁止該信號。PHY 必須確保 MII_CS 信號在沖突條件下保持有效狀態。該信號無需與 TX 和 RX 時鐘保持同步。在全雙工模式下,該信號沒意義。

MII_COL:沖突檢測信號。檢測到介質上存在沖突后,PHY 必須立即使能沖突檢測信號,并且只要存在沖突條件,沖突檢測信號必須保持有效狀態。該信號無需與 TX 和 RX 時鐘保持同步。在全雙工模式下,該信號沒意義。

MDC:MDC信號屬于SMI接口,具體請看《STM32網絡之SMI接口》。

MDIO:MDIO信號屬于SMI接口,具體請看《STM32網絡之SMI接口》。

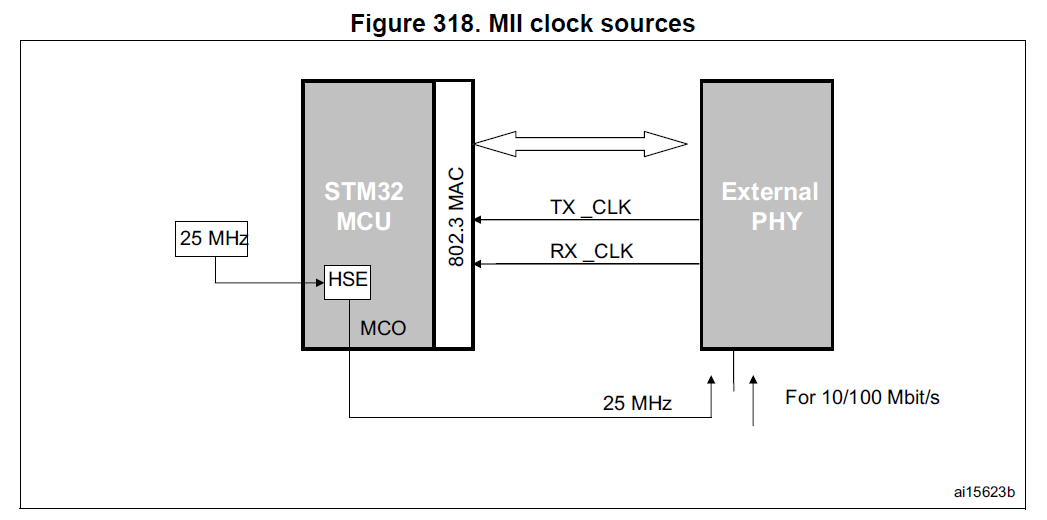

下圖TX接口信號編碼

下圖RX 接口信號編碼

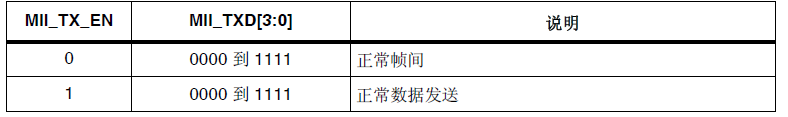

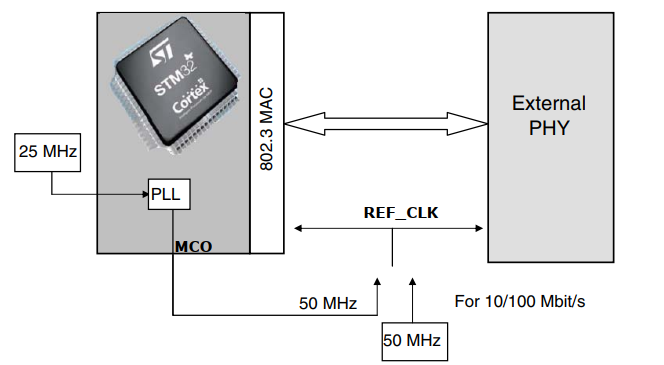

MII接口的時鐘源

要生成TX_CLK 和RX_CLK 時鐘信號,必須向外部PHY 提供25MHz 時鐘,如圖所 示。除了使用外部 25 MHz石英晶體提供該時鐘,還可以通過STM32F20xx 微控制器的MCO引腳輸出該信號。這種情況下,必須對PLL 倍頻進行配置,以通過25 MHz 外部石英晶體在MCO 引腳上獲得所需頻率。

對應的代碼

/* Enable GPIOs clocks */ RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA,ENABLE); /* Enable SYSCFG clock */ RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE); /* Configure MCO (PA8) */ GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStructure.GPIO_OType = GPIO_OType_PP; GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL ; GPIO_Init(GPIOA, &GPIO_InitStructure); /* Output HSE clock (25MHz) on MCO pin (PA8) to clock the PHY */ RCC_MCO1Config(RCC_MCO1Source_HSE, RCC_MCO1Div_1);

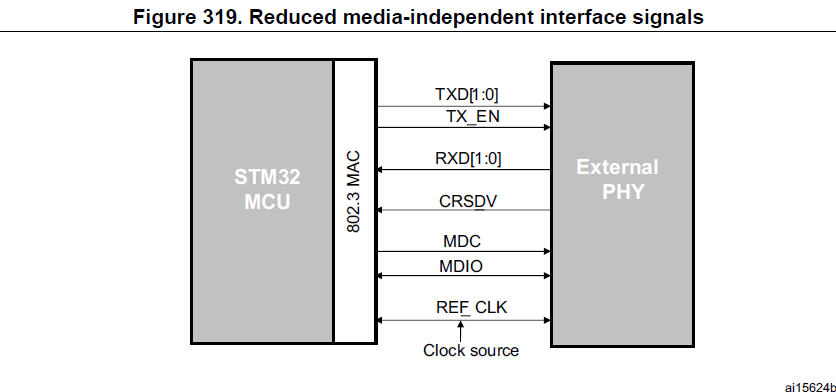

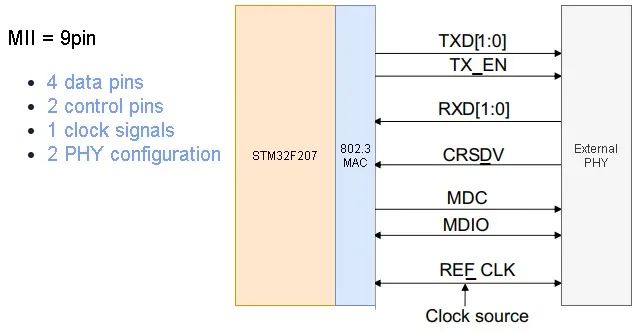

Reduced media-independent interface: RMII(精簡介質獨立接口)。精簡介質獨立接口(RMII) 規范降低了10/100 Mbit/s 下微控制器以太網外設與外部PHY 間的引腳數。

根據IEEE 802.3u 標準,MII包括16 個數據和控制信號的引腳。RMII規范將引腳數減少為 7 個(引腳數減少62.5%)。引腳的含義參考MII接口即可。

RMII接口是MAC和PHY之間的實例化對象。這些有助于MAC的MII接口轉化為RMII接口。RMII接口具有以下特點

10-Mbit/s 和 100-Mbit/s 的運行速率

參考時鐘必須是 50 MHz

相同的參考時鐘必須從外部提供給 MAC 和外部以太網 PHY

它提供了獨立的 2 位寬(雙位)的發送和接收數據路徑

這里時鐘管腳比MII接口少,有一個非常重要的點,那就是RMII接口時鐘源必須是50MHZ

RMII接口時鐘源

STM32F207xx控制器可以從MCO引腳提供50MHz時鐘信號,當然用戶需要配置PLL來產生這一時鐘。

使用外部50 MHz 時鐘驅動PHY 或使用嵌入式PLL 生成50 MHz 頻率信號來驅動PHY。

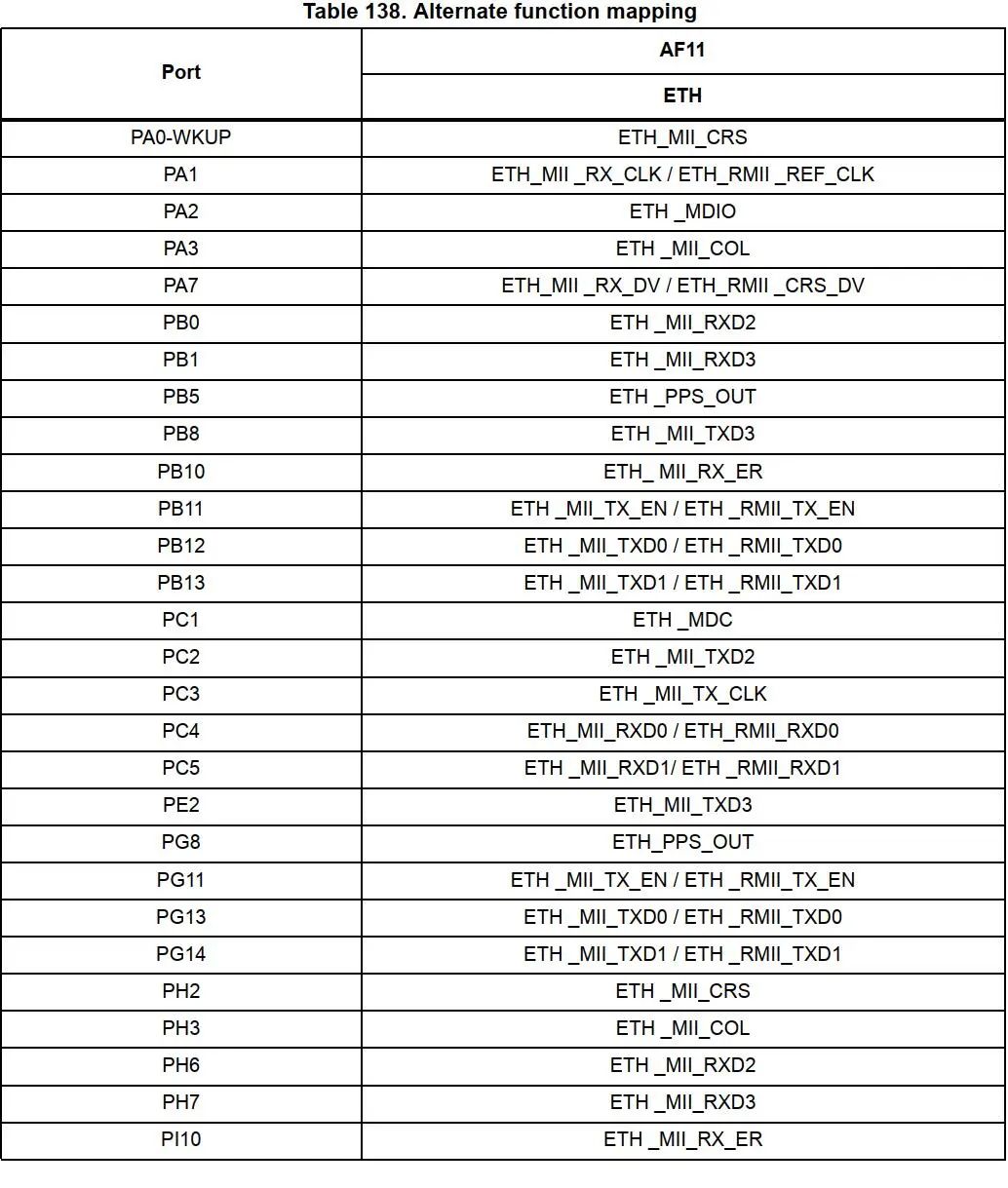

STM32F207VCT6(100pin)的芯片

Ethernet pins configuration ETH_MDIO -------------------------> PA2 pin 25 ETH_MDC --------------------------> PC1 pin 16 ETH_PPS_OUT ----------------------> PB5 pin 91 ETH_MII_CRS ----------------------> PA0 pin 23 ETH_MII_COL ----------------------> PA3 pin 26 ETH_MII_RX_ER --------------------> PB10 pin 47 ETH_MII_RXD2 ---------------------> PB0 pin 35 ETH_MII_RXD3 ---------------------> PB1 pin 36 ETH_MII_TX_CLK -------------------> PC3 pin 18 ETH_MII_TXD2 ---------------------> PC2 pin 17 ETH_MII_TXD3 ---------------------> PB8 pin 95 ETH_MII_RX_CLK/ETH_RMII_REF_CLK---> PA1 pin 24 ETH_MII_RX_DV/ETH_RMII_CRS_DV ----> PA7 pin 32 ETH_MII_RXD0/ETH_RMII_RXD0 -------> PC4 pin 33 ETH_MII_RXD1/ETH_RMII_RXD1 -------> PC5 pin 34 ETH_MII_TX_EN/ETH_RMII_TX_EN -----> PB11 pin 48 ETH_MII_TXD0/ETH_RMII_TXD0 -------> PB12 pin 51 ETH_MII_TXD1/ETH_RMII_TXD1 -------> PB13 pin 52

其中ETH_PPS_OUT這個管腳ST官方demo屏蔽,不屬于MII接口也不屬于RMII接口。下面不將其統計進入。

MII 共15個接口加上SMI接口,共17個引腳。(沒有包含25MHz時鐘的引腳)

RMII共7個接口加上SMI接口,共9個引腳。

除了上述我自行統計的MII接口和RMII接口對應的pin之外,ST官方在參考手冊也給出了對應圖,如下:

使用SYSCFG_PMC 寄存器(注意:這里和F107不同,F107是AFIO_MAPR寄存器)中的23配置位MII_RMII_SEL選擇MII 或RMII 模式。以太網控制器處于復位模式或使能時鐘前,應用程序必須設置MII/RMII 模式。

對應的ST庫函數為

//函數入參可選以下 //SYSCFG_ETH_MediaInterface_MII: MII mode selected //SYSCFG_ETH_MediaInterface_RMII: RMII mode selected void SYSCFG_ETH_MediaInterfaceConfig(uint32_t SYSCFG_ETH_MediaInterface)

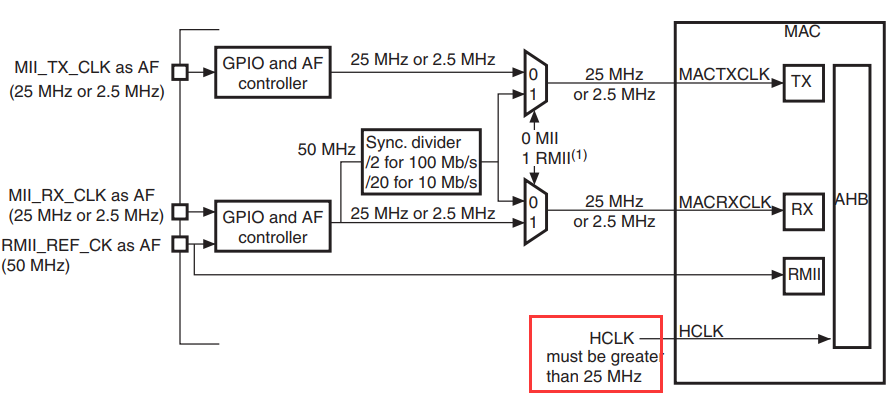

MII/RMII 內部時鐘方案

支持MII 和RMII 以及10 和100 Mbit/s 運行所需的時鐘方案,如下圖所示。

注意上圖紅框中:HCLK必須大于25MHz,這個問題點,在上一篇文章《STM32網絡之SMI接口》中已經提到了,這里再次提到,如果不滿足這個條件,可能會出現奇奇怪怪的問題,不好查找。

在官方手冊中,還有一句

要節省引腳,需在同一個GPIO 引腳上復用RMII_REF_CK 和MII_RX_CLK 這兩個輸入時鐘信號。

以上是“STM32網絡中MII和RMII接口有什么用”這篇文章的所有內容,感謝各位的閱讀!希望分享的內容對大家有幫助,更多相關知識,歡迎關注億速云行業資訊頻道!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。