您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇文章為大家展示了Circuitjs中怎么創建一個自定義邏輯器件,內容簡明扼要并且容易理解,絕對能使你眼前一亮,通過這篇文章的詳細介紹希望你能有所收獲。

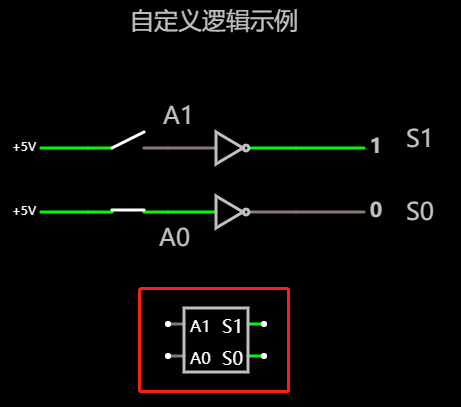

來看一個具體的示例, 通過它來講述 自定義邏輯 是什么, 為什么以及怎么去做.

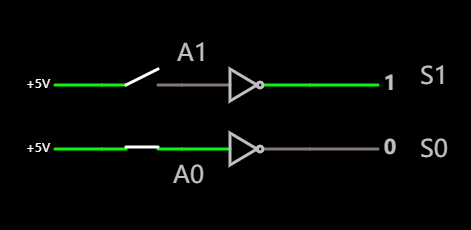

這個示例如下, 兩個輸入 A1 和 A0, 兩個輸出 S1 和 S0, 兩者間的關系也很簡單, 就是對輸入簡單取反, 因此使用了兩個 非門 就達到了目的.

輸出與輸入間的關系就是:

S1=!A1 S0=!A0

其中感嘆號 ! 表示取反.

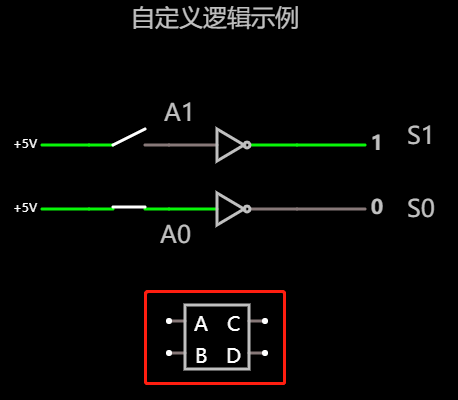

上述的邏輯是用電路直接實現, 現在假設要使用自定義邏輯的方式去做一個等價實現, 從而取代上述 非門 構成的電路, 要怎么去做呢?

至于為什么引入自定義邏輯, 放在后面再解釋.

第一步是添加一個自定義邏輯器件, 在菜單或右鍵中選擇 添加自定義邏輯, 然后拖動生成一個缺省的自定義邏輯器件:

默認情況, 它包含兩個輸入 A 和 B, 兩個輸出 C 和 D, 但這只是缺省情況, 可以進一步調整, 輸入和輸出均可以是一個或多個, 而不是限于兩個.

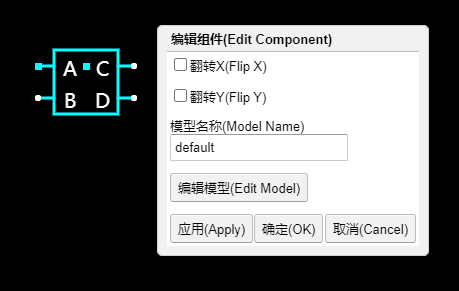

下一步是雙擊(或"右鍵--編輯")組件編輯其屬性:

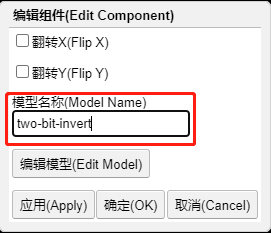

首先給它一個名稱, 比如"two-bit-invert":

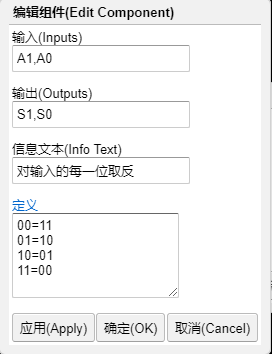

接著點擊 編輯模型, 在彈出窗口中, 有四個屬性可以編輯, 分別為 輸入, 輸出, 信息文本, 定義, 下面將一一說明:

輸入

改為

A1,A0, 與原型一致, 以(英文)逗號分隔. 當然, 這里實際叫什么并不是特別重要, 根據你自己需要去定義即可, 但建議盡可能簡短.視具體情況不同, 輸入端可以有更多或更少. 比如

X,Y,Z就表示有三個輸入端, 名稱分別被設為 X, Y 和 Z.

輸出

改為

S1,S0, 與原型一致(同理, 這里實際叫什么也不是特別重要)同樣的, 輸出端也不限于兩個, 可以更多或更少.

信息文本

這里可以填入對功能的一個具體描述, 比如"對輸入的每一位取反"

定義

這是最重要的, 它定義了輸入輸出間的邏輯關系.

怎么定義呢? 最簡單方式就是枚舉所有輸入的組合情況, 并給出對應輸出的值.

如果你有數字電路基礎, 很明顯這跟所謂的 真值表(True Table) 就是一回事.

那么對于前述取反邏輯, 最終的定義如下:

00=11 01=10 10=01 11=00

最終如下:

等號左邊對應輸入, 右邊對應輸出.

第一行, 左邊 00 分別表示 A1=0, A0=0, 右邊 11 表示 S1=1, S0=1;

第二行, 左邊 01 分別表示 A1=0, A0=1, 右邊 10 表示 S1=1, S0=0;

第三行, 左邊 10 分別表示 A1=1, A0=0, 右邊 01 表示 S1=0, S0=1;

第四行, 左邊 11 分別表示 A1=1, A0=1, 右邊 00 表示 S1=0, S0=0;

很顯然, 以上通過枚舉所有輸入(及對應的輸出)情況, 表達了前述的取反邏輯:

S1=!A1 S0=!A0

如果創建另一個自定義邏輯, 并有如下定義:

00=0 01=1 10=1 11=1

那么就是定義了一個具有兩個輸入端, 一個輸出端的邏輯組件.

顯然, 上述定義實際上就是一個 或門.

同樣的, 還可以定義更復雜的如異或門, 半加器, 全加器, 譯碼器以及其它你想要的邏輯組件等等.

確定之后, 組件按我們定義的輸入, 輸出名稱顯示如下, 當鼠標移上去后, 畫布的右下角還將顯示對應名稱及信息文本:

接下來可以測試其是否滿足相應邏輯, 如果不能滿足, 則可能需要仔細檢查 定義 里的規則是否有誤; 如果一切 OK, 則可以用它取代兩個非門構成的電路.

自然, 對于簡單的, 容易實現的邏輯來說, 自定義邏輯并沒有什么優勢;

但對于更復雜一些, 更多輸入, 輸出的情況, 你可能一下子想不出用電路怎么去實現, 又或者能用電路實現, 但非常龐雜, 各種組件, 連線非常多, 這時自定義邏輯就有優勢了.

最終, 所有的邏輯還是要落到具體的電路實現上, 自定義邏輯有時更像是一種"投機取巧", 但用得好, 它還是可以輔助你在整體設計期間, 先忽略部分模塊的具體實現, 不至于迷失在過多的細節里, 你可以假設這些子部件是已經實現的, 然后測試整體的邏輯是否 OK.

當大的框架及交互沒有問題時, 你可以回過頭來再一一去實現那些自定義邏輯, 所以, 它也可以幫你推遲某些實現, 但又不影響整體的功能.

每個自定義邏輯器件都有一個模型名稱, 該名稱指向描述其工作方式的模型.

您可以創建具有相同型號的任意數量的器件.

編輯模型會更改使用該模型的所有器件的行為.

編輯模型時, 可以指定輸入, 輸出, 一些信息文本(將鼠標懸停在器件上時顯示在右下角)和定義.

輸入(和輸出)是(英文)逗號分隔的短引腳標簽列表(最多一個或兩個字符).

您還可以指定 取反標簽, 像 /Q 對應 <span >Q</span>.

示例:A,B,/C,/D

定義是形式為多行的 輸入=輸出.

與輸入引腳匹配的第一個輸入模式將被選中, 并將輸出引腳設置為與輸出模式匹配.

模式可以包含比特值(0, 1), 過渡(+, -), 通配符/任意值(?), 和模式字母(A, B, 等等).

輸入必須不少于輸入引腳的數量.

如果更長, 則會將額外的模式字符與輸出引腳進行匹配;這使您可以創建帶有狀態的器件.

輸出模式還可包含 _, 以指示高阻抗狀態.

前面舉的具體示例代表了最基本, 最常用的情況, 但自定義邏輯還支持更復雜的表達方式, 比如通配之類的; 甚至, 除了組合邏輯外, 你還可以定義時序邏輯組件.

下面是一些具體示例及說明.

輸入: A,B,C

輸出: X

定義:

111=0 ???=1

如果所有三個輸入均為 1, 則輸出為 0. 否則為 1.

輸入: A,B,C

輸出: S,C

定義:

111=11 110=10 011=10 101=10 100=01 010=01 001=01 000=00

輸入: S,R

輸出: Q,/Q

定義:

?? 00=10 10 ??=10 01 ??=01 ?? AB=AB

輸入模式(等號的左側)按順序匹配 S, R, Q 和 <span >Q</span>.

等號右側指定對應的 Q 和 <span >Q</span> 結果值.

第一行, 如果兩個輸入均為低電平, 則將 Q 輸出置位(復位電路時需要此設置).

第二行, 如果 置位端(set) 為高, 則將輸出設置為 1,0.

第三行, 如果 復位端(reset) 為高, 則將輸出設置為 0,1.

第四行, 除以上情況外, 將使輸出保持不變.

前兩個字母與輸入引腳匹配, 后兩個字母與輸出引腳匹配.

空格會被忽略, 此處添加空格僅為清晰起見.

輸入: D,Clk

輸出: Q,/Q

定義:

?? 00=10 0+ ??=01 1+ ??=10 ?? AB=AB

如果兩個輸入均為低電平, 則第一行將 Q 輸出置位(復位電路時需要此設置).

接下來的兩行在時鐘的上升沿時將 Q 輸出設置為與 D 輸入匹配.

除以上情況外, 最后一行使輸出保持不變.

輸入: J,K,Clk

輸出: Q,/Q

定義:

??? 00=10 00- AB=AB 10- ??=10 01- ??=01 11- AB=BA ??? AB=AB

如果兩個輸入均為低電平, 則第一行將 Q 輸出置位(復位電路時需要此設置).

接下來的四行在時鐘的負跳變上實現JK觸發器邏輯.

除以上情況外, 最后一行使輸出保持不變.

輸入: A2,A1,A0,B2,B1,B0

輸出: Eq,A>,A<

定義:

ABC ABC=100 1?? 0??=010 A1? A0?=010 AB1 AB0=010 ??? ???=001

第一行檢查兩個輸入是否相等. 接下來的三行測試 A 是否更大. 否則, B 更大.

輸入: Clk

輸出: A,B,C

定義:

+ AB0=AB1 + A01=A10 + 011=100 + 111=000 ? ABC=ABC

該計數器在 Clk 輸入的正跳變時遞增計數.

第一行處理從 000、010、100 或 110 開始的計數.

第二行處理從 001 或 101 開始的計數.

接下來的兩行處理 011 和 111.

最后一行確保除非時鐘產生正跳變, 否則輸出不會改變.

輸入: A,B,C,En

輸出: X

定義:

1111=0 ???1=1 ???0=_

與上面的 3 輸入與非門相同, 不同之處在于如果 使能引腳 為低電平, 則輸出進入高阻抗狀態.

輸入: A,En

輸出: X

定義:

A1=A ?0=_

上述內容就是Circuitjs中怎么創建一個自定義邏輯器件,你們學到知識或技能了嗎?如果還想學到更多技能或者豐富自己的知識儲備,歡迎關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。