您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

米爾科技推出的MYD-CZU3EG開發板搭載的就是UltraScale+ MPSoC平臺器件 — XCZU3EG,它集成了四核Cortex-A53 處理器,雙核 Cortex-R5 實時處理單元以及Mali-400 MP2 圖形處理單元及 16nm FinFET+ 可編程邏輯相結合的異構處理系統,具有高性能,低功耗,高擴展等特性,除了這款異構SOC之外,板子還搭載了豐富的接口和完善的開發資料,下面我們來一探究竟。

開箱

暖色調的簡潔外包裝上印有一行“Make Your idea Real”。

開箱之后就是擺放在內襯中的板卡和配套設備。除了板卡之外,配套的電源、數據線、SD卡和光盤等等,可謂考慮齊全。

板卡資源介紹

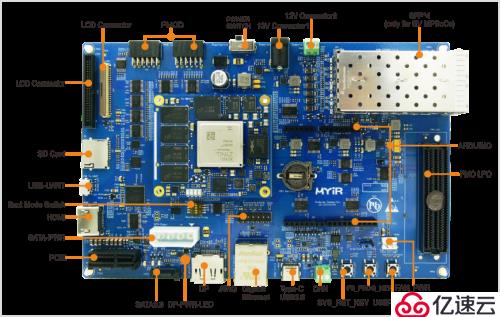

筆者迫不及待的拆開板卡的防靜電袋。MYD-CZU3EG 開發板由MYC-CZU3EG 核心板加MYB-CZU3EG 底板組成。散熱器下面是核心板,這是一個CPU最小系統模塊,集成了主處理器和存儲。底板是一塊外設接口板,集成了電源和多種接口,方便評估或集成。

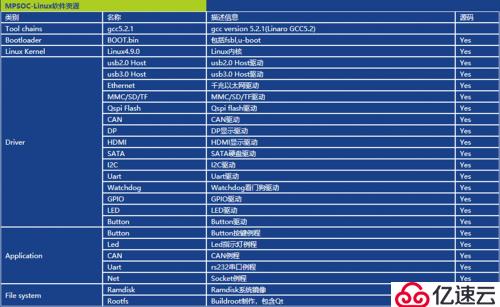

下面我們詳細的了解一下板卡詳細的組成結構,首先,核心板基于Xilinx XCZU3EG全可編程處理器,4核Cortex-A53(Up to 1.5GHZ)+FPGA(154K LE),具體型號:XCZU3EG-1SFVC784,(未來可選配XCZU2CG, XCZU3CG,XCZU4EV,XCZU5EV),性能強大;板載4GB DDR4 SDRAM(64bit,2400MHZ) 及豐富的存儲資源,從容應對復雜運算;板載千兆以太網PHY 和USB PHY , 輕松實現高速互聯,如此奢華的配置,板子尺寸只有62*50mm,令人贊嘆。

另外,板子選材和用料講究,據稱使用了Intel電源模塊,松下的M6 PCB板材,Micron存儲,村田電容,還是非常良心的。

底板的外設接口豐富,板載了串口,網口,HDMI,DP,SATA,PCIE,USB3.0 Type-C,LCD,PMOD,Arduino,FMC-LPC,TF 卡接口,SFP,ADC,CAN等多種接口,方便用戶評估或集成。這些接口根據SOC的結構,有的接在PS端,有的接在PL端。

PS 單元:

Zynq UltraScale+ MPSoC介紹

1.真正的全可編程異構多處理SOC

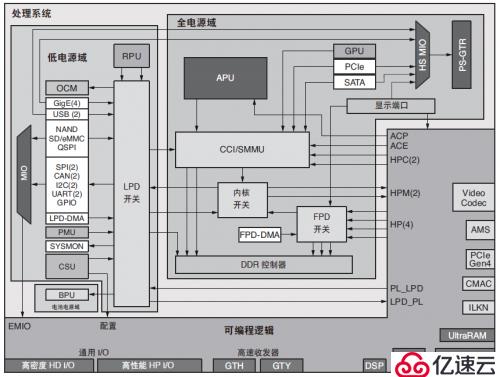

在使用板子之前,我們先來了解一下這款板卡的核心芯片——XCZU3EG,這是Xilinx繼ZYNQ-7000系列之后推出的真正的全可編程異構平臺,Zynq? UltraScale+ MPSoC 器件不僅提供 64 位處理器可擴展性,同時還將實時控制與軟硬件引擎相結合,支持圖形、視頻、波形與數據包處理。置于包含通用實時處理器和可編程邏輯的平臺上,三個不同變體包括雙應用處理器 (CG) 器件、四核應用處理器和 GPU (EG) 器件、以及視頻編解碼器 (EV) 器件, 為 5G 無線、下一代 ADAS 和工業物聯網創造了無限可能性。

MYD-CZU3EG開發套件目前搭載的是EG,后期還可以選配CG或EV器件。EG 器件采用運行速率高達 1.5GHz 的四核 ARM? Cortex-A53 平臺與雙核 Cortex-R5 實時處理器、Mali-400 MP2 圖形處理單元及 16nm FinFET+ 可編程邏輯相結合。

該開發板有著無與倫比的集成度、高性能和低功耗特點,與 Zynq-7000 SoC 相比,系統級性能功耗比提升5 倍,為交付最低系統功耗而精心設計,官方給出的典型應用包括基帶 L1 加速、公共安全與移動無線電和8x8 100 MHz TD-LTE 遠端射頻單元等場景。

說到應用,不得不提Zynq UltraScale+ MPSoC最最擅長的領域——面向視頻編解碼器和圖形引擎的前沿多媒體解決方案。賽靈思SoC為多媒體解決方案提供了多種支持,包括:

EV 器件帶有集成型 GPU 和H.264 / H.265視頻編解碼器,專為超高清 (UHD) 視頻而設計帶有集成型 H.264 / H.265 視頻編解碼器,能夠同時編解碼達 4Kx2K (60fps) 的視頻,可實現單芯片4K視頻處理,當然MYD-CZU3EG開發板使用的是EG器件,沒有視頻編解碼器,但是有Mali-400 MP2 GPU。

Mali-400 MP2 GPU與 APU 直接綁定,還可在幀緩存中加速視頻圖形渲染,從而實現顯示器輸出。GPU 可通過獨立的并行引擎進行像素渲染,速度遠高于依靠 CPU 來處理圖形,而且與需要設計人員添加片外 GPU 引擎的解決方案相比,成本與功耗均更低。GPU 通過全面可編程的架構加速 2D 和 3D 圖形,該架構既支持基于著色器的圖形 API ,也支持固定功能圖形 API 。GPU 具有抗鋸齒功能,能實現最佳圖像質量,且幾乎不會造成額外的性能損耗。Xilinx配套提供經實踐檢驗的全套 Linux 驅動程序,能自動將圖形命令從 APU 轉到 CPU 處理。

另外,Zynq UltraScale+ MPSoC 提供高速互聯外設,后者包含集成式 DisplayPort 接口模塊。DisplayPort接口位于 PS 端,可多路復用至四個專用高速串行收發器中的兩個,工作速率高達 6 Gb/s。該架構擺脫了對于額外顯示芯片的需求,進一步降低了系統 BOM 成本。

DisplayPort 接口基于 VESA DisplayPort Standard Version 1 和 Revision 2a 開發,其提供的多個接口能處理來自 PS 或 PL 的實時音視頻流,也能存儲來自存儲器幀緩存的音視頻。它同時支持兩個音視頻流水線,支持 alpha 混合、chroma 復采樣、色彩空間轉換和音頻混合等功能的動態渲染。DisplayPort 既可使用一個 PS PLL,也能使用 PL 的時鐘生成像素時鐘。

除視頻編解碼器和圖形處理之外,多媒體應用還需要其他重要組件,如視頻數據的輸入輸出管理 , 以及處理高速視頻數據的功能。在 PL 內可設計定制化邏輯,用于捕獲來自直播源的視頻。例如,SDI RX、HDMI RX、MIPI CSI IP 等協議均可用于捕獲不同來源的原始視頻。視覺算法可用于采集來自原始數據的重要信息,如路標識別和針對駕駛員輔助技術的動作檢測、視頻監控面部識別、高級拍攝應用的物體與動作識別等。除收集數據外,算法還可用于音視頻廣播和視頻會議等用例中處理與操控原始數據。考慮到今后幾年視頻分辨率不可避免的攀升態勢,有關算法需要具備極高的工作速度。PL 為此類算法提供了所需的硬件加速功能,便于大幅提高性能,滿足下一代技術需求。

Zynq UltraScale+ MPSoC 的靈活性能加速計算密集型應用程序,在 GPU、CPU 和 PL 之間共享工作負載,在 PL 中可卸載復雜的算數計算以實現硬件加速,并且在 APU 上可預先計算 OpenGL 著色語言 (GLSL) 一致變量。GPU 著色器核心上的計算僅適用于頂點和片斷之間不同的值。整批頂點中所有保持常量的值在 CPU 上處理最為有效。

Zynq UltraScale+ MPSoC 在設計之初就考慮了高效電源管理問題,該器件被分為四個電源域:

Zynq UltraScale+ MPSoC 含有可控制電源域的創新型平臺管理單元 (PMU),。PMU 負責器件的安全管理,并監管電源域內的電源。不用的電源域可在啟動時關閉,然后智能地通過中斷或事件喚醒,實現精細的電源管理。

我們已經知道Zynq UltraScale+ MPSoC 內部分了多個處理核心,四核ARM Cortex-A53是應用處理單元,具有高效的基線性能,適合Linux應用處理;雙核 ARM Cortex-R5是實時處理單元理想適用于低時延確定性應用,諸如安全模塊和 APU 任務分擔等,另外圖形引擎,高速外設等針對特定應用做了優化,各個模塊各司其職,系統性能明顯提升。該器件采用了臺積電 (TSMC) 的 16nm FinFET 工藝節點,。該工藝節點采用更高效的晶體管實現方案,具備最佳的開關速度以及比平面工藝更低的漏電流,因此能實現更高性能和更低功耗。從 28nm 的 Zynq-7000 到 16nm 的 Zynq UltraScale+ MPSoC,性能提升了 60%,功耗降低 20%,使原始處理器性能提升 2.7 倍。

示例

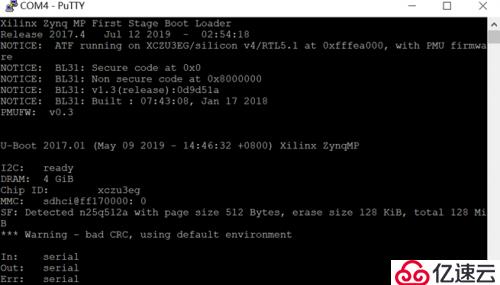

板子QSPI閃存預先燒錄了Linux鏡像,默認也是從QSPI閃存啟動的,使用數據線連接板子串口和PC,連接電源,板子上電,打開putty,可以看到系統啟動信息。通過命令行可以登錄,默認密碼是root。

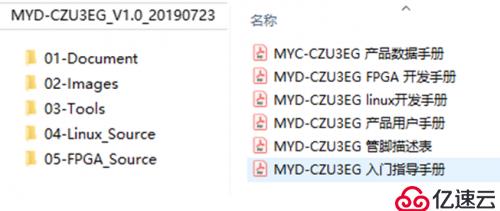

光盤中也提供了系統的鏡像文件,用戶如果不熟悉Linux系統編譯,可以直接使用。

另外,MYD-CZU3EG 光盤中提供了常用外設的演示程序,例如:

這里我們使用Xilinx Vivado新建一個HelloWorld工程,生成啟動鏡像,從TF卡啟動。整個過程分為:

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。