您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

一個4位計數器程序在ISE 聯合modelsim進行仿真,代碼如下

testbench的內容:

module count4_tb;

reg clk,reset;

wire [3:0] out;

parameter DELY=100;

count4 mycount(out,reset,clk);

always #(DELY/2) clk=~clk;

initial begin

clk=0;

reset=0;

#DELY reset=1;

#DELY reset=0;

#(DELY*200) $finish;

end

initial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);

endmodule

count4.v的內容:

module count4(out,reset,clk

);

output [3:0] out;

input reset,clk;

reg [3:0] out;

always@(posedge clk) begin

if(reset)

out<=0;

else

out<=out+1;

end

endmodule

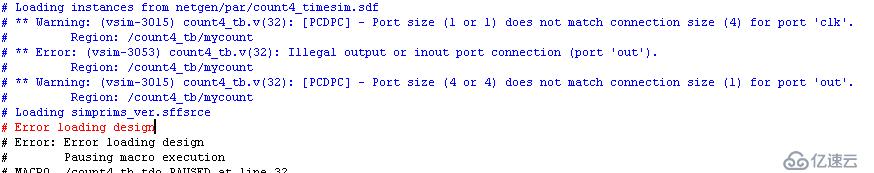

功能仿真,沒有錯誤,而布局布線后仿真,有如下錯誤提示

改正辦法:

將testbench 中的 count4 mycount(out,reset,clk);改為count4 mycount(.out(out),.reset(reset),.clk(clk));時序仿真就會正確運行。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。